### PRODUCT/PROCESS CHANGE NOTIFICATION

PCN APM/10/6004 Notification Date 11/04/2010

Conversion to ECOPACK 2 for products housed in: DPAK, IPAK, PPAK, D2PAK, I2PAK and P2PAK packages in the ST plants

### **Table 1. Change Implementation Schedule**

| Forecasted implementation date for change                                                    | 24-Jan-2011 |

|----------------------------------------------------------------------------------------------|-------------|

| Forecasted availabillity date of samples for customer                                        | 28-Oct-2010 |

| Forecasted date for <b>STMicroelectronics</b> change Qualification Plan results availability | 28-Oct-2010 |

| Estimated date of changed product first shipment                                             | 03-Feb-2011 |

### **Table 2. Change Identification**

| Product Identification (Product Family/Commercial Product) | See attached list                                                                                                                                                                                                                                                                                                                                                                   |

|------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Type of change                                             | Package assembly material change                                                                                                                                                                                                                                                                                                                                                    |

| Reason for change                                          | To implement massive ECOPACK 2                                                                                                                                                                                                                                                                                                                                                      |

| Description of the change                                  | To move from standard to massive production of ECOPACK 2 graded supply and complete the move to Copper wire bonding. The changes here reported will not affect the electrical, dimensional and thermal parameters keeping unchanged all information reported on the relevant datasheets. There is as well no change in the packing process nor in the standard delivery quantities. |

| Product Line(s) and/or Part Number(s)                      | See attached                                                                                                                                                                                                                                                                                                                                                                        |

| Description of the Qualification Plan                      | See attached                                                                                                                                                                                                                                                                                                                                                                        |

| Change Product Identification                              | ECOPACK 2 grade identification printed on the inner and external box labels                                                                                                                                                                                                                                                                                                         |

| Manufacturing Location(s)                                  |                                                                                                                                                                                                                                                                                                                                                                                     |

**47/**.

| _  |     | _ |       | _  | _    | _   |      |   |

|----|-----|---|-------|----|------|-----|------|---|

| Tэ | hla | 3 | l iet | Λf | Atta | chn | nant | c |

|    |     |   |       |    |      |     |      |   |

| Customer Part numbers list |  |

|----------------------------|--|

| Qualification Plan results |  |

| Customer Acknowledgement of Receipt                       | PCN APM/10/6004              |

|-----------------------------------------------------------|------------------------------|

| Please sign and return to STMicroelectronics Sales Office | Notification Date 11/04/2010 |

| □ Qualification Plan Denied                               | Name:                        |

| □ Qualification Plan Approved                             | Title:                       |

|                                                           | Company:                     |

| □ Change Denied                                           | Date:                        |

| □ Change Approved                                         | Signature:                   |

| Remark                                                    |                              |

|                                                           |                              |

|                                                           |                              |

|                                                           |                              |

|                                                           |                              |

|                                                           |                              |

|                                                           |                              |

|                                                           |                              |

|                                                           |                              |

|                                                           |                              |

**47/**.

### **DOCUMENT APPROVAL**

| Name              | Function                   |

|-------------------|----------------------------|

| Mottese, Anna     | Division Marketing Manager |

| Riviera, Antonio  | Division Marketing Manager |

| Naso, Lorenzo     | Division Product Manager   |

| Wilson, lan       | Division Product Manager   |

| Falcone, Giuseppe | Division Q.A. Manager      |

| Motta, Antonino   | Division Q.A. Manager      |

4/48

#### Premise

The ECOPACK<sup>®</sup> program is the cornerstone of our effort of being a leader in the change toward environmentally friendly packaging. In the context of this program, ST develops world class technical solutions designed to progressively remove banned substances from manufacturing.

Continuing in the already announced plan of moving the supply to the ECOPACK<sup>®</sup>2 grade products (also known in the market as "Halogen Free") and in the aim of a constant process improvement, DPAK, IPAK, PPAK, D<sup>2</sup>PAK, I<sup>2</sup>PAK and P<sup>2</sup>PAK packages will be from now available as ECOPACK<sup>®</sup>2 graded.

#### WHY THIS CHANGE?

To implement massive **ECOPACK**<sup>®</sup>**2** grade supply DPAK, IPAK, PPAK, D<sup>2</sup>PAK, I<sup>2</sup>PAK and P<sup>2</sup>PAK packages. This PCN is intended as well, for announcing the completion of the switch for the remaining products using different bonding material, to Copper Wire as communicated by previous CPCN documents DSG-TRA/04/395 and MPA-PWR/06/1963. These packages version, will be entirely manufactured in the ST's premises.

#### **WHAT IS THE CHANGE?**

To move from standard to massive production of ECOPACK®2 graded supply and complete the move to Copper wire bonding.

The changes here reported will not affect the electrical, dimensional and thermal parameters keeping unchanged all information reported on the relevant datasheets.

There is as well no change in the packing process nor in the standard delivery quantities.

#### WHEN?

For the products listed in the attached document, the availability will be granted according the following schedule:

| Product Family       | Package/s | Samples       | <b>Full Production</b> |

|----------------------|-----------|---------------|------------------------|

| Voltage Regulators   | All       | Wk 43 (*) '10 | Wk 04 '11              |

| Power MOSFET         | All       | Wk 43 (*) '10 | Wk 04 '11              |

| Power Bipolar & IGBT | All       | Wk 43 (*) '10 | Wk 04 ' 11             |

(\*) For Test Vehicle – For other samples please contact Marketing

### **Change implementation schedule:**

The conversion to ECOPACK<sup>®</sup>2 grade, due to the huge quantities are affected by this change, will be not done in a single step but according to Customer requirements and material availability and will initiate from January 2011. During this transition phase, unless specific Customer-related instructions, ST's is willing to ship either the standard or the ECOPACK<sup>®</sup>2 grade supply.

### Marking and traceability:

Unless otherwise stated by customer specific requirement, ECOPACK®2 grade parts will be identified by the relevant data code and the related ECOPACK®2 grade identification printed on the inner and external box labels.

#### **Qualification Data:**

Qualification reports are in the appendix here attached.

Please note that ST Team is doing all the best for providing you full visibility about these announced changes and to minimize any negative impact it may occur.

While our Marketing and Sales teams are available for additional information when required, we are looking forward to your renewed confidence in STMicroelectronics as the strategic partner of your choice.

--

REL-6043-058 W 10

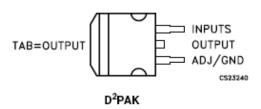

### **Reliability Evaluation Report** D<sup>2</sup>PAK

HF Epoxy Resin

**General Information**

**Product Line** LUAD

**Product Description** RZDJ\*LUADFC1 P/N LD1085D2T-R\$2Z

**Product Group** APM **Product division** VR **Package** D<sup>2</sup>PAK Silicon Process technology **Bipolar**  Locations

Wafer fab Singapore Assembly plant

Shenzhen

Reliability Lab Site Reliability Lab

Catania

Reliability assessment Pass

#### **DOCUMENT INFORMATION**

| Version | Date         | Pages | Prepared by                      | Approved by     | Comment |

|---------|--------------|-------|----------------------------------|-----------------|---------|

| 1.0     | 23 Feb. 2010 | 7     | Alfio Rao<br>Giuseppe Giacopello | Giovanni Presti | Final   |

Note: This report is a summary of the reliability trials performed in good faith by STMicroelectronics in order to evaluate the potential reliability risks during the product life using a set of defined test methods.

This report does not imply for STMicroelectronics expressly or implicitly any contractual obligations other than as set forth in STMicroelectronics general terms and conditions of Sale. This report and its contents shall not be disclosed to a third party without previous written agreement from STMicroelectronics.

**REL-6043-058 W 10**

### **TABLE OF CONTENTS**

| 1 | APPLICABLE AND REFERENCE DOCUMENTS |                               |   |  |  |  |  |

|---|------------------------------------|-------------------------------|---|--|--|--|--|

|   | GLOSSARY                           |                               |   |  |  |  |  |

|   |                                    | ABILITY EVALUATION OVERVIEW   |   |  |  |  |  |

| - | 3.1                                | Objectives                    |   |  |  |  |  |

|   | 3.2                                | Conclusion                    |   |  |  |  |  |

| 4 |                                    | CE CHARACTERISTICS            |   |  |  |  |  |

|   | 4.1                                | DEVICE DESCRIPTION            |   |  |  |  |  |

|   | 4.2                                | CONSTRUCTION NOTE             | 4 |  |  |  |  |

| 5 |                                    | TS RESULTS SUMMARY            |   |  |  |  |  |

|   | 5.1                                | TEST VEHICLE                  | 5 |  |  |  |  |

|   | 5.2                                | TEST PLAN AND RESULTS SUMMARY | 5 |  |  |  |  |

| 6 | ANNI                               | EXES                          | € |  |  |  |  |

|   | 6.1                                | DEVICE DETAILS                |   |  |  |  |  |

|   | 6.2                                | TESTS DESCRIPTION             | 7 |  |  |  |  |

REL-6043- 058 W 10

### 1 APPLICABLE AND REFERENCE DOCUMENTS

| Document reference | Short description                                       |  |

|--------------------|---------------------------------------------------------|--|

| JESD47             | Stress-Test-Driven Qualification of Integrated Circuits |  |

### **2 GLOSSARY**

| <b>DUT</b> Device Under Test |              |

|------------------------------|--------------|

| SS                           | Sample Size  |

| HF                           | Halogen Free |

### **3 RELIABILITY EVALUATION OVERVIEW**

### 3.1 Objectives

D2PAK qualification using HF Epoxy Resin

### 3.2 Conclusion

Qualification Plan requirements have been fulfilled without exception. It is stressed that reliability tests have shown that the devices behave correctly against environmental tests (no failure). Moreover, the stability of electrical parameters during the accelerated tests demonstrates the ruggedness of the products and safe operation, which is consequently expected during their lifetime.

REL-6043-058 W 10

### **4 DEVICE CHARACTERISTICS**

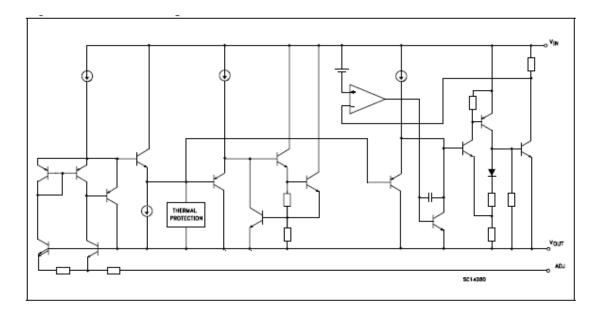

### 4.1 Device description

The LD1085xx is a low drop voltage regulator able to provide up to 3 A of output current.

Dropout is guaranteed at a maximum of 1.2 V at the maximum output current, decreasing at lower loads. The LD1085xx is pin to pin compatible with the older 3-terminal adjustable regulators, but has better performances in term of drop and output tolerance.

A 2.85 V output version is suitable for SCSI-2 active termination. Unlike PNP regulators, where a part of the output current is wasted as quiescent current, the LD1085xx quiescent current flows into the load, so increase efficiency. Only a  $10 \, \mu F$  minimum capacitor is need for stability.

### 4.2 Construction note

|                                           | <b>P/N</b> LD1085                       |

|-------------------------------------------|-----------------------------------------|

| Wafer/Die fab. information                |                                         |

| Wafer fab manufacturing location          | Singapore                               |

| Technology                                | BIPOLAR                                 |

| Die finishing back side                   | Cr/Ni/Au                                |

| Die size                                  | 3.13x2.36mm                             |

| Bond pad metallization layers             | 1                                       |

| Passivation type                          | SiN                                     |

| Wafer Testing (EWS) information           |                                         |

| Electrical testing manufacturing location | APEE Asia Pac EWS                       |

| Tester                                    | QT200                                   |

| Test program                              | 7139629                                 |

| Assembly information                      |                                         |

| Assembly site                             | STS Shenzhen                            |

| Package description                       | D <sup>2</sup> PAK                      |

| Molding compound                          | HF Epoxy Resin                          |

| Frame material                            | TO263 Dt 40u Ver7 OptF/G selected NiNiP |

| Die attach process                        | Soft solder                             |

| Die attach material                       | Pb95.5Ag2.5Sn2 (5XP92057)               |

| Die pad size                              | 5.38x6.48mm                             |

| Wire bonding process                      | Thermosonic Bonding                     |

| Wires bonding materials/diameters         | 2.0mils Cu wire                         |

| Lead finishing process                    | Pure tin plating                        |

|                                           |                                         |

| Final testing information                 |                                         |

| Testing location                          | STS                                     |

| Tester                                    | QT200                                   |

| Test program                              | 7490171                                 |

REL-6043- 058 W 10

### **5 TESTS RESULTS SUMMARY**

### 5.1 Test vehicle

| Lot # | Diffusion<br>Lot | Assy Lot   | Process/<br>Package | Product Line | Comments |

|-------|------------------|------------|---------------------|--------------|----------|

| 1     | V685002T         | GK9310A201 | D <sup>2</sup> PAK  | LUAD         |          |

### 5.2 Test plan and results summary

**P/N** LD1085

|          | THE ED 1000        |                 |                                                                                       |     |        |            |                        |  |  |

|----------|--------------------|-----------------|---------------------------------------------------------------------------------------|-----|--------|------------|------------------------|--|--|

| Test     | РС                 | Std ref.        | Conditions                                                                            | SS  | Steps  | Failure/SS | Note                   |  |  |

| Die Orie | Die Oriented Tests |                 |                                                                                       |     |        |            |                        |  |  |

|          |                    | JESD22          |                                                                                       |     | 168 H  | 0/45       |                        |  |  |

| HTSL     | HTSL N             | A-103           | Ta = 150℃                                                                             |     | 500 H  | 0/45       |                        |  |  |

|          |                    | A-103           |                                                                                       |     | 1000 H | 0/45       |                        |  |  |

|          |                    | JESD22          |                                                                                       |     | 168 H  | 0/45       | onginooring            |  |  |

| HTSL     | Ν                  | JESD22<br>A-103 | Ta = 175℃                                                                             |     | 500 H  | 0/45       | engineering evaluation |  |  |

|          | A-103              |                 |                                                                                       |     | 1000 H | 0/45       | evaluation             |  |  |

| Package  | Orie               | ented Tests     |                                                                                       | _   | -      |            | _                      |  |  |

| PC       |                    | JESD22<br>A-113 | Drying 24 H @ 125℃<br>Store 168 H @ Ta=85℃ Rh=85%<br>Oven Reflow @ Tpeak=260℃ 3 times | 160 | Final  | Pass       |                        |  |  |

| AC       | Υ                  | JESD22<br>A-102 | Pa=2Atm / Ta=121℃                                                                     |     | 168 H  | 0/77       |                        |  |  |

|          |                    | IESD33          |                                                                                       |     | 100 cy | 0/77       |                        |  |  |

| TC       | Υ                  | JESD22<br>A-104 | Ta = -65℃ to 150℃                                                                     |     | 200 cy | 0/77       |                        |  |  |

|          |                    | A-104           |                                                                                       |     | 500 cy | 0/77       |                        |  |  |

REL-6043- 058 W 10

### **6 ANNEXES**

### 6.1 Device details

### 6.1.1 Pin connection

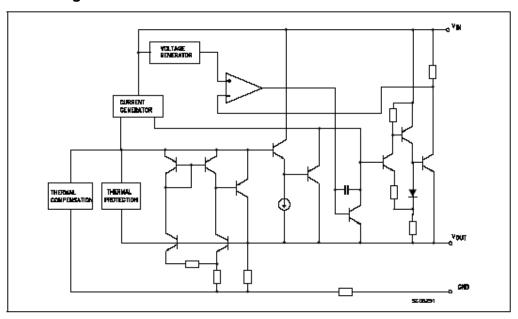

### 6.1.2 Block diagram

REL-6043- 058 W 10

### 6.2 Tests Description

| Test name                                | Description                                                                                                                         | Purpose                                                                                                                                                                                                                                                                                                                               |

|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Die Oriented                             |                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                       |

| HTSL<br>High Temperature<br>Storage Life | the max. temperature allowed by the                                                                                                 | To investigate the failure mechanisms activated<br>by high temperature, typically wire-bonds solder<br>joint ageing, data retention faults, metal stress-<br>voiding.                                                                                                                                                                 |

| Package Oriented                         |                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                       |

| <b>PC</b><br>Preconditioning             | The device is submitted to a typical temperature profile used for surface mounting devices, after a controlled moisture absorption. | As stand-alone test: to investigate the moisture sensitivity level. As preconditioning before other reliability tests: to verify that the surface mounting stress does not impact on the subsequent reliability performance. The typical failure modes are "pop corn" effect and delamination.                                        |

| AC Auto Clave (Pressure Pot)             | The device is stored in saturated steam, at fixed and controlled conditions of pressure and temperature.                            | To investigate corrosion phenomena affecting die or package materials, related to chemical contamination and package hermeticity.                                                                                                                                                                                                     |

| TC<br>Temperature<br>Cycling             | The device is submitted to cycled temperature excursions, between a hot and a cold chamber in air atmosphere.                       | To investigate failure modes related to the thermo-mechanical stress induced by the different thermal expansion of the materials interacting in the die-package system. Typical failure modes are linked to metal displacement, dielectric cracking, molding compound delamination, wire-bonds failure, die-attach layer degradation. |

Quality and Reliability

July 2010 REL-6043-232 W 10

Reliability Evaluation Report

DPAK Package

HF Epoxy Resin

**General Information**

Product Line LUAD

Product Description 3 A low-drop, adjustable

positive voltage regulator

P/N LD1085CDT-R

Product Group MSH

Product division IPC

Package DPAK

Silicon Process technology B30II

Locations

Wafer fab Singapore

Assembly plant SHENZHEN

Reliability Lab

IMS-APM Catania

Reliability Lab

Reliability assessment PASS

#### **DOCUMENT INFORMATION**

| Version | Date        | Pages | Prepared by    | Approved by     | Comment     |

|---------|-------------|-------|----------------|-----------------|-------------|

| 1.0     | 12-Jul-2010 | 8     | Alfio Riciputo | Giovanni Presti | First issue |

Note: This report is a summary of the reliability trials performed in good faith by STMicroelectronics in order to evaluate the potential reliability risks during the product life using a set of defined test methods.

This report does not imply for STMicroelectronics expressly or implicitly any contractual obligations other than as set forth in STMicroelectronics general terms and conditions of Sale. This report and its contents shall not be disclosed to a third party without previous written agreement from STMicroelectronics.

Quality and Reliability

July 2010 REL-6043-232 W 10

### **TABLE OF CONTENTS**

| 1 | APPI | LICABLE AND REFERENCE DOCUMENTS | 3 |

|---|------|---------------------------------|---|

| 2 | GLO  | SSARY                           | 3 |

|   |      | ABILITY EVALUATION OVERVIEW     |   |

|   | 3.1  | Objectives                      | 3 |

|   | 3.2  | Conclusion                      | 3 |

|   | 3.3  | DEVICE DESCRIPTION              | 4 |

|   |      | CONSTRUCTION NOTE               |   |

| 4 | TEST | TS RESULTS SUMMARY              | 5 |

|   | 4.1  | TEST VEHICLE                    | 5 |

|   | 4.2  | TEST PLAN AND RESULTS SUMMARY   | 5 |

| 5 | ANN  | EXES                            | 6 |

|   | 5.1  | DEVICE DETAILS                  | 6 |

|   | 5.2  | Tests Description               | 0 |

July 2010 REL-6043-232 W 10

Quality and Reliability

### 1 APPLICABLE AND REFERENCE DOCUMENTS

| Document reference | Short description                                       |

|--------------------|---------------------------------------------------------|

| JESD47             | Stress-Test-Driven Qualification of Integrated Circuits |

### **2 GLOSSARY**

| DUT | Device Under Test |

|-----|-------------------|

| HF  | Halogen Free      |

### **3 RELIABILITY EVALUATION OVERVIEW**

### 3.1 Objectives

To qualify DPAK package using HF Epoxy Resin.

### 3.2 Conclusion

Qualification Plan requirements have been fulfilled without exception. It is stressed that reliability tests have shown that the devices behave correctly against environmental tests (no failure). Moreover, the stability of electrical parameters during the accelerated tests demonstrates the ruggedness of the products and safe operation, which is consequently expected during their lifetime.

Quality and Reliability

July 2010 REL-6043-232 W 10

3.3 Device description

3 A low-drop, adjustable positive voltage regulator

### 3.4 Construction note

|                                           | LD10                      | 085           |  |  |  |

|-------------------------------------------|---------------------------|---------------|--|--|--|

|                                           | LOT1                      | LOT2          |  |  |  |

| Wafer/Die fab. information                |                           |               |  |  |  |

| Wafer fab manufacturing location          | Singapore                 |               |  |  |  |

| Technology                                | B30                       | OII .         |  |  |  |

| Die finishing back side                   | Cr/Ni                     | /Au           |  |  |  |

| Die size                                  | 3.13x2.3                  | 36 mm         |  |  |  |

| Passivation type                          | Sil                       | N             |  |  |  |

| Wafer Testing (EWS) information           |                           |               |  |  |  |

| Electrical testing manufacturing location | APEE Asia Pa              | EWS 0899      |  |  |  |

| Tester                                    | QT2                       | 00            |  |  |  |

| Test program                              | LUXXEP**.CT               | S ver. WAD    |  |  |  |

| Assembly information                      |                           |               |  |  |  |

| Assembly site                             | SHENZ                     | ZHEN          |  |  |  |

| Package description                       | DPA                       | AK            |  |  |  |

| Molding compound                          | HF Epoxy Resin            | Epoxy resin   |  |  |  |

| Frame material                            | FRAME TO251 \             | /e7 OpD SelNi |  |  |  |

| Die attach process                        | Soft solder               |               |  |  |  |

| Die attach material                       | Pb95.5Ag2.5Sn2 (5XP92057) |               |  |  |  |

| Die pad size                              | 3.00 x 4.20 mm            |               |  |  |  |

| Wire bonding process                      | Thermosoni                | c Bonding     |  |  |  |

| Wires bonding materials/diameters         | 2.0mils (                 |               |  |  |  |

| Lead finishing process                    | Pure tin plating          |               |  |  |  |

| Final testing information                 |                           |               |  |  |  |

| Testing location                          | SHENZ                     | ZHEN          |  |  |  |

| Tester                                    | QT2                       | 00            |  |  |  |

| Test program                              | 7490                      | 171           |  |  |  |

Quality and Reliability

July 2010 REL-6043-232 W 10

**4 TESTS RESULTS SUMMARY**

### 4.1 Test vehicle

| Lot # | Diffusion Lot | Assy Lot   | Technical Code | Package | Product Line | Comments                    |

|-------|---------------|------------|----------------|---------|--------------|-----------------------------|

| 1     | V60006L7      | GK0170KV0B | - BZGR*LUADFC1 | DPAK    | LUAD         | Epoxy resin<br>Halogen free |

| 2     | V60096L7      | GK0170KV0A |                |         | LUAD         | Epoxy resin                 |

### 4.2 Test plan and results summary

#### LD1085

| _        | טוט:            |                 |                                                                                          |      |        |       | 10.0  |      |

|----------|-----------------|-----------------|------------------------------------------------------------------------------------------|------|--------|-------|-------|------|

| Test     | est PC Std ref. |                 | Conditions                                                                               | SS   | Steps  | Failu | re/SS | Note |

| 1631     | . 0             | ota rei.        | Conditions                                                                               | - 00 | Oteps  | Lot 1 | Lot 2 | Note |

| Die Orie | nted            | Tests           |                                                                                          |      |        |       |       |      |

|          |                 | JESD22          |                                                                                          |      | 168 H  | 0/45  | 0/45  |      |

| HTSL     | N               | A-103           | Ta = 150℃                                                                                |      | 500 H  | 0/45  | 0/45  |      |

|          |                 | A-103           |                                                                                          |      | 1000 H | 0/45  | 0/45  |      |

| Package  | Orie            | nted Tests      |                                                                                          |      |        |       |       |      |

| PC       |                 | JESD22<br>A-113 | Drying 24 H @ 125℃<br>Store 168 H @ Ta=85℃ Rh=85%<br>Oven Reflow @ Tpeak=260℃<br>3 times |      | Final  | Pass  | Pass  |      |

| AC       | Υ               | JESD22<br>A-102 | Pa=2Atm / Ta=121℃                                                                        |      | 168 H  | 0/77  | 0/77  |      |

|          |                 | IECDOO          |                                                                                          |      | 100 cy | 0/77  | 0/77  |      |

| TC       | Υ               | JESD22<br>A-104 | Ta = -65℃ to 150℃                                                                        |      | 200 cy | 0/77  | 0/77  |      |

|          |                 | A-104           |                                                                                          |      | 500 cy | 0/77  | 0/77  |      |

|          |                 | IECDOO          | To 05% DII 050/                                                                          |      | 168 H  | 0/77  | 0/77  |      |

| THB      | Υ               | JESD22          | Ta = 85℃, RH = 85%,<br>Vbias= +24V                                                       |      | 500 H  | 0/77  | 0/77  |      |

|          |                 | A-101           | VDIAS= +24V                                                                              |      | 1000 H | 0/77  | 0/77  |      |

Quality and Reliability

### **5** ANNEXES

### 5.1 Device details

### 5.1.1 Pin connection

### 5.1.2 Block diagram

Quality and Reliability

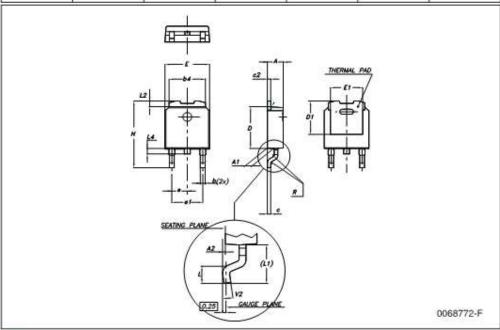

### 5.1.3 Package outline/Mechanical data

| Dim  |      | mm.  |      |       | inch. |       |

|------|------|------|------|-------|-------|-------|

| Dim. | Min. | Тур. | Max. | Min.  | Тур.  | Max.  |

| A    | 2.2  |      | 2.4  | 0.086 |       | 0.094 |

| A1   | 0.9  |      | 1.1  | 0.035 |       | 0.043 |

| A2   | 0.03 |      | 0.23 | 0.001 |       | 0.009 |

| В    | 0.64 |      | 0.9  | 0.025 | 2     | 0.035 |

| b4   | 5.2  |      | 5.4  | 0.204 |       | 0.212 |

| С    | 0.45 |      | 0.6  | 0.017 |       | 0.023 |

| C2   | 0.48 |      | 0.6  | 0.019 |       | 0.023 |

| D    | 6    |      | 6.2  | 0.236 |       | 0.244 |

| D1   | 1    | 5.1  |      |       | 0.200 |       |

| E    | 6.4  |      | 6.6  | 0.252 | -     | 0.260 |

| E1   |      | 4.7  |      |       | 0.185 |       |

| е    |      | 2.28 |      |       | 0.090 |       |

| e1   | 4.4  |      | 4.6  | 0.173 |       | 0.181 |

| Н    | 9.35 |      | 10.1 | 0.368 |       | 0.397 |

| L    | 1    |      |      | 0.039 |       |       |

| (L1) |      | 2.8  |      |       | 0.110 |       |

| L2   |      | 0.8  |      |       | 0.031 |       |

| L4   | 0.6  |      | 1    | 0.023 |       | 0.039 |

| R    |      | 0.2  |      |       | 0.008 |       |

| V2   | 0.0  |      | 8°   | 0°    |       | 89    |

Quality and Reliability

July 2010 REL-6043-232 W 10

### 5.2 Tests Description

| Test name                                | Description                                                                                                                                                               | Purpose                                                                                                                                                                                                                                                                                                                               |

|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Die Oriented                             |                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                       |

| HTSL<br>High Temperature<br>Storage Life | the max. temperature allowed by the                                                                                                                                       | To investigate the failure mechanisms activated<br>by high temperature, typically wire-bonds solder<br>joint ageing, data retention faults, metal stress-<br>voiding.                                                                                                                                                                 |

| Package Oriented                         |                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                       |

| <b>PC</b><br>Preconditioning             | The device is submitted to a typical temperature profile used for surface mounting devices, after a controlled moisture absorption.                                       | As stand-alone test: to investigate the moisture sensitivity level.  As preconditioning before other reliability tests: to verify that the surface mounting stress does not impact on the subsequent reliability performance.  The typical failure modes are "pop corn" effect and delamination.                                      |

| AC                                       | The device is stored in saturated steam, at                                                                                                                               | To investigate corrosion phenomena affecting                                                                                                                                                                                                                                                                                          |

| Auto Clave                               | fixed and controlled conditions of pressure                                                                                                                               |                                                                                                                                                                                                                                                                                                                                       |

| (Pressure Pot)                           | and temperature.                                                                                                                                                          | contamination and package hermeticity.                                                                                                                                                                                                                                                                                                |

| <b>TC</b><br>Temperature<br>Cycling      | The device is submitted to cycled temperature excursions, between a hot and a cold chamber in air atmosphere.                                                             | To investigate failure modes related to the thermo-mechanical stress induced by the different thermal expansion of the materials interacting in the die-package system. Typical failure modes are linked to metal displacement, dielectric cracking, molding compound delamination, wire-bonds failure, die-attach layer degradation. |

| THB Temperature Humidity Bias            | The device is biased in static configuration minimizing its internal power dissipation, and stored at controlled conditions of ambient temperature and relative humidity. | To evaluate the package moisture resistance with electrical field applied, both electrolytic and galvanic corrosion are put in evidence.                                                                                                                                                                                              |

Industrial & Power Conversion

Quality and Reliability

REL-6043-336 W 10

## Reliability Evaluation Report DPAK Package

HF Epoxy Resin

**General Information**

Product Line KSAD

Product Description RGGR\*KSADAA6

**P/N** LD1117DTTR

Product Group APM-MSH

Product division IPC VR

Package DPAK

Silicon Process technology BIPOLAR

Locations

Wafer fab Singapore

Assembly plant LGG

Reliability Lab

Catania Reliability Lab

Reliability assessment Pass

#### **DOCUMENT INFORMATION**

| Version | Date            | Pages | Prepared by | Approved by     | Comment      |

|---------|-----------------|-------|-------------|-----------------|--------------|

| 1.0     | 12 October 2010 | 8     | Alfio Rao   | Giovanni Presti | Final Report |

Note: This report is a summary of the reliability trials performed in good faith by STMicroelectronics in order to evaluate the potential reliability risks during the product life using a set of defined test methods.

This report does not imply for STMicroelectronics expressly or implicitly any contractual obligations other than as set forth in STMicroelectronics general terms and conditions of Sale. This report and its contents shall not be disclosed to a third party without previous written agreement from STMicroelectronics.

### Industrial & Power Conversion Quality and Reliability

REL-6043-336 W 10

### **TABLE OF CONTENTS**

| 1  | APPL | LICABLE AND REFERENCE DOCUMENTS | 3 |

|----|------|---------------------------------|---|

|    |      | SSARY                           |   |

|    |      | ABILITY EVALUATION OVERVIEW     |   |

|    |      | Objectives                      |   |

|    | 3.2  | CONCLUSION                      | 3 |

| DE |      | CHARACTERISTICS                 |   |

|    | 3.3  | DEVICE DESCRIPTION              |   |

|    | 3.4  | CONSTRUCTION NOTE               | 4 |

| 4  | TEST | S RESULTS SUMMARY               | 5 |

|    |      | TEST VEHICLE.                   |   |

|    |      | TEST PLAN AND RESULTS SUMMARY   |   |

| 5  | ANNE | EXES                            | 6 |

| •  | 5.1  | DEVICE DETAILS                  | 6 |

|    | 5.2  | TESTS DESCRIPTION               | 8 |

Industrial & Power Conversion

Quality and Reliability

REL-6043-336 W 10

### 1 APPLICABLE AND REFERENCE DOCUMENTS

| Document reference | Short description                                       |

|--------------------|---------------------------------------------------------|

| JESD47             | Stress-Test-Driven Qualification of Integrated Circuits |

### **2 GLOSSARY**

| DUT | Device Under Test |

|-----|-------------------|

| SS  | Sample Size       |

| HF  | Halogen Free      |

### **3 RELIABILITY EVALUATION OVERVIEW**

### 3.1 Objectives

To qualify DPAK line using Epoxy resin Halogen free. Test Vehicle: *KSAD - LD1117DTTR*

### 3.2 Conclusion

Qualification Plan requirements have been fulfilled without exception. It is stressed that reliability tests have shown that the devices behave correctly against environmental tests (no failure). Moreover, the stability of electrical parameters during the accelerated tests demonstrates the ruggedness of the products and safe operation, which is consequently expected during their lifetime.

Industrial & Power Conversion

Quality and Reliability

REL-6043-336 W 10

### **DEVICE CHARACTERISTICS**

### 3.3 Device description

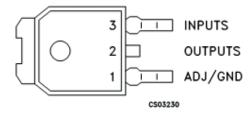

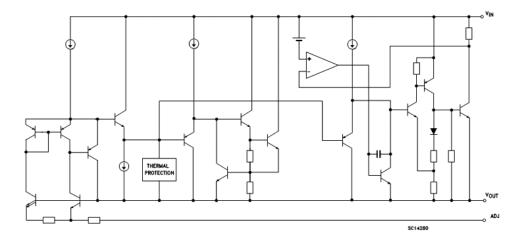

The LD1117 is a low drop voltage regulator able to provide up to 800 mA of output current, available even in adjustable version (VREF = 1.25 V). Concerning fixed versions, are offered the following output voltages: 1.2 V, 1.8 V, 2.5 V, 2.85 V, 3.0 V, 3.3 V and 5.0 V. The 2.85 V type is ideal for SCSI-2 lines active termination.

### 3.4 Construction note

|                                           | P/N: LD1117DTTR                 |

|-------------------------------------------|---------------------------------|

| Wafer/Die fab. information                |                                 |

| Wafer fab manufacturing location          | Singapore                       |

| Technology                                | Bipolar                         |

| Die finishing back side                   | Cr/Ni/Au                        |

| Die size                                  | 1990x1860µm                     |

| Passivation type                          | SiN                             |

| Wafer Testing (EWS) information           |                                 |

| Electrical testing manufacturing location | APEE Asia Pac EWS               |

| Tester                                    | QT200                           |

| Test program                              | KSXXEQXX.CTS vers. WAD          |

| Assembly information                      |                                 |

| Assembly site                             | LGG                             |

| Package description                       | DPAK                            |

| Molding compound                          | HF Epoxy Resin                  |

| Die attach process                        | SOLF SOLDER                     |

| Die attach material                       | Pb/Ag/Sn 95.5/2.5/2 D.76mm      |

| Die pad size                              | 3.0x4.2mm                       |

| Wire bonding process                      | Thermosonic Bonding Copper wire |

| Wires bonding materials/diameters         | 1.5mils Cu wire                 |

| Lead finishing/bump solder material       | 100% Sn plating                 |

| Final testing information                 |                                 |

| Testing location                          | STS                             |

| Tester                                    | QT200                           |

| Test program                              | KSX2FAAD.CTS                    |

### Industrial & Power Conversion Quality and Reliability

REL-6043-336 W 10

### **4 TESTS RESULTS SUMMARY**

### 4.1 Test vehicle

P/N: LD1117DTTR

| Lot<br># | Diffusion<br>Lot | Assy Lot | Process/<br>Package | Product Line | Comments |

|----------|------------------|----------|---------------------|--------------|----------|

| 1        | V6007EE7         | KSAD01G  |                     |              |          |

| 2        | V6007EE7         | KSAD02G  | DPAK                | KSAD         |          |

| 3        | V6004KLJ         | KSAD03G  |                     |              |          |

### 4.2 Test plan and results summary

P/N: LD1117DTTR

| Toot               | DC.   | Ctd not               | Conditions                                                                               | SS Steps Failure/SS |        |       | Note  |       |      |

|--------------------|-------|-----------------------|------------------------------------------------------------------------------------------|---------------------|--------|-------|-------|-------|------|

| Test               | PC    | Std ref. Conditions S |                                                                                          | 33                  | Steps  | Lot 1 | Lot 2 | Lot 3 | Note |

| Die Oriented Tests |       |                       |                                                                                          |                     |        |       |       |       |      |

|                    |       | JESD22                |                                                                                          |                     | 168 H  | 0/77  | -     | -     |      |

| HTB                | N     | A-108                 | Tj = 125℃, BIAS= +15 V                                                                   |                     | 500 H  | 0/77  | -     | -     |      |

|                    |       | A-100                 |                                                                                          |                     | 1000 H | 0/77  | -     | -     |      |

|                    |       | JESD22                |                                                                                          |                     | 168 H  | 0/45  | 0/45  | 0/45  |      |

| HTSL               | N     | A-103                 | Ta = 150°C                                                                               |                     | 500 H  | 0/45  | 0/45  | 0/45  |      |

|                    |       | A-103                 |                                                                                          |                     | 1000 H | 0/45  | 0/45  | 0/45  |      |

| Package            | e Ori | ented Tests           |                                                                                          |                     |        |       |       |       |      |

| PC                 |       | JESD22<br>A-113       | Drying 24 H @ 125℃<br>Store 168 H @ Ta=85℃ Rh=85%<br>Oven Reflow @ Tpeak=260℃ 3<br>times |                     | Final  | Pass  | Pass  | Pass  |      |

| AC                 | Υ     | JESD22<br>A-102       | Pa=2Atm / Ta=121℃                                                                        |                     | 168h   | 0/77  | 0/77  | 0/77  |      |

|                    |       | JESD22                |                                                                                          |                     | 100 cy | 0/77  | 0/77  | 0/77  |      |

| TC                 | Υ     |                       | A-104 Ta = -65°C to 150°C                                                                |                     | 200 cy | 0/77  | 0/77  | 0/77  |      |

|                    |       | A-10 <del>-1</del>    |                                                                                          |                     | 500 cy | 0/77  | 0/77  | 0/77  |      |

|                    |       | JESD22                | Ta = 85℃, RH = 85%,                                                                      |                     | 168 H  | 0/77  | 0/77  | 0/77  |      |

| THB                | Υ     | A-101                 | BIAS= +12 V                                                                              |                     | 500 H  | 0/77  | 0/77  | 0/77  |      |

|                    |       | 7. 101                | DIA3= +12 V                                                                              |                     | 1000 H | 0/77  | 0/77  | 0/77  |      |

Industrial & Power Conversion

Quality and Reliability

REL-6043-336 W 10

### **5 ANNEXES**

### 5.1 Device details

### 5.1.1 Pin connection

Pin connections (top view)

### 5.1.2 Block diagram

### Industrial & Power Conversion Quality and Reliability

REL-6043-336 W 10

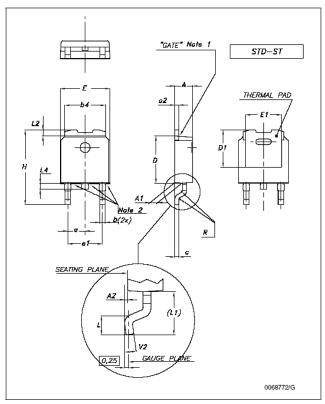

### 5.1.3 Package outline/Mechanical data

|      | Type STD-ST |      |       |  |  |  |

|------|-------------|------|-------|--|--|--|

| Dim. | mm.         |      |       |  |  |  |

|      | Min.        | Тур. | Max.  |  |  |  |

| Α    | 2.20        |      | 2.40  |  |  |  |

| A1   | 0.90        |      | 1.10  |  |  |  |

| A2   | 0.03        |      | 0.23  |  |  |  |

| b    | 0.64        |      | 0.90  |  |  |  |

| b4   | 5.20        |      | 5.40  |  |  |  |

| С    | 0.45        |      | 0.60  |  |  |  |

| c2   | 0.48        |      | 0.60  |  |  |  |

| D    | 6.00        |      | 6.20  |  |  |  |

| D1   |             | 5.10 |       |  |  |  |

| E    | 6.40        |      | 6.60  |  |  |  |

| E1   |             | 4.70 |       |  |  |  |

| е    |             | 2.28 |       |  |  |  |

| e1   | 4.40        |      | 4.60  |  |  |  |

| Н    | 9.35        |      | 10.10 |  |  |  |

| L    | 1.00        |      |       |  |  |  |

| L1   |             | 2.80 |       |  |  |  |

| L2   |             | 0.80 |       |  |  |  |

| L4   | 0.60        |      | 1.00  |  |  |  |

| R    |             | 0.20 |       |  |  |  |

| V2   | 0°          |      | 8°    |  |  |  |

- Note: 1 Maximum resin gate protrusion: 0.5 mm.

- Maximum resin protrusion: 0.25 mm.

### Industrial & Power Conversion Quality and Reliability

REL-6043-336 W 10

### 5.2 Tests Description

| Test name                                | Description                                                                                                                                                               | Purpose                                                                                                                                                                                                                                                                                                                               |

|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Die Oriented                             |                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                       |

| HTB<br>High Temperature<br>Bias          | The device is stressed in static or dynamic configuration, approaching the operative max. absolute ratings in terms of junction temperature and bias condition.           | To determine the effects of bias conditions and temperature on solid state devices over time. It simulates the devices' operating condition in an accelerated way.  The typical failure modes are related to, silicon degradation, wire-bonds degradation, oxide faults.                                                              |

| HTSL<br>High Temperature<br>Storage Life | The device is stored in unbiased condition at<br>the max. temperature allowed by the<br>package materials, sometimes higher than<br>the max. operative temperature.       | g .                                                                                                                                                                                                                                                                                                                                   |

| Package Oriented                         |                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                       |

| <b>PC</b><br>Preconditioning             | The device is submitted to a typical temperature profile used for surface mounting devices, after a controlled moisture absorption.                                       | As stand-alone test: to investigate the moisture sensitivity level.  As preconditioning before other reliability tests: to verify that the surface mounting stress does not impact on the subsequent reliability performance.  The typical failure modes are "pop corn" effect and delamination.                                      |

| AC Auto Clave (Pressure Pot)             | The device is stored in saturated steam, at fixed and controlled conditions of pressure and temperature.                                                                  | To investigate corrosion phenomena affecting die or package materials, related to chemical contamination and package hermeticity.                                                                                                                                                                                                     |

| TC<br>Temperature<br>Cycling             | The device is submitted to cycled temperature excursions, between a hot and a cold chamber in air atmosphere.                                                             | To investigate failure modes related to the thermo-mechanical stress induced by the different thermal expansion of the materials interacting in the die-package system. Typical failure modes are linked to metal displacement, dielectric cracking, molding compound delamination, wire-bonds failure, die-attach layer degradation. |

| THB Temperature Humidity Bias            | The device is biased in static configuration minimizing its internal power dissipation, and stored at controlled conditions of ambient temperature and relative humidity. | To evaluate the package moisture resistance with electrical field applied, both electrolytic and galvanic corrosion are put in evidence.                                                                                                                                                                                              |

# Reliability Report On DPAK package with halogen free resin

**General Information**

Product Lines BA19-B653-3L2S-EL6C-EZ60-

EZ62-EZ82

Product Description

N-Channel Power MOSFET

NPN Power BIPOLAR

MJD3055T4 MJD45H11T4 STD20NF06LT4

STD100NH02LT4 STD2HNK60Z

STD4NK60ZT4 STD3NK80ZT4

Product Group IMS – APM

Product division Power Transistor Division

Package DPAK

**Commercial Products**

Silicon Process technology

N-Channel Power MOSFET

NPN Power BIPOLAR

|                 | Locations                            |

|-----------------|--------------------------------------|

| Wafer fab       | BA19 / B653/ EZ82/ EZ60<br>Singapore |

|                 | EL6C / EZ62 /3L2S<br>Catania (ITALY) |

| Assembly plant  | LONGGANG (China)<br>SHENZHEN (China) |

| Reliability Lab | IMS-APM Catania Reliability Lab      |

### **DOCUMENT INFORMATION**

| Version | Date         | Pages | Prepared by             | Approved by | Comment     |

|---------|--------------|-------|-------------------------|-------------|-------------|

| 1.0     | October-2010 | 18    | G.Montalto<br>G De Luca | G.Falcone   | First issue |

|         |              |       |                         |             |             |

|         |              |       |                         |             |             |

Note: This report is a summary of the reliability trials performed in good faith by STMicroelectronics in order to evaluate the potential reliability risks during the product life using a set of defined test methods.

This report does not imply for STMicroelectronics expressly or implicitly any contractual obligations other than as set forth in STMicroelectronics general terms and conditions of Sale. This report and its contents shall not be disclosed to a third party without previous written agreement from STMicroelectronics.

### **TABLE OF CONTENTS**

| 1 | APP  | PLICABLE AND REFERENCE DOCUMENTS          | 3  |

|---|------|-------------------------------------------|----|

|   |      | DSSARY                                    |    |

|   |      | IABILITY EVALUATION OVERVIEW              |    |

|   |      | Objectives                                |    |

|   | 3.2  | CONCLUSION                                | 3  |

|   |      | ICE CHARACTERISTICS                       |    |

|   | 4.1  | DEVICE DESCRIPTION                        | 4  |

|   | 4.2  | CONSTRUCTION NOTE                         | 4  |

| 5 |      | TS RESULTS SUMMARY                        |    |

|   |      | Test vehicle                              |    |

|   |      | RELIABILITY TEST PLAN AND RESULTS SUMMARY |    |

| A | NNEX | (ES 6.0                                   | 18 |

|   | 6 1T | ESTS DESCRIPTION                          | 18 |

### 1 APPLICABLE AND REFERENCE DOCUMENTS

| Document reference | Short description                                       |

|--------------------|---------------------------------------------------------|

| JESD47             | Stress-Test-Driven Qualification of Integrated Circuits |

|                    |                                                         |

### 2 GLOSSARY

| DUT | Device Under Test |

|-----|-------------------|

| SS  | Sample Size       |

| HF  | Halogen Free      |

### **3 RELIABILITY EVALUATION OVERVIEW**

### 3.1 Objectives

Qualifications of DPAK package with halogen free resin.

### 3.2 Conclusion

The reliability tests have shown that the devices behave correctly against environmental tests (no failure). Moreover, the stability of electrical parameters during the accelerated tests demonstrates the ruggedness of the products and safe operation, which is consequently expected during their lifetime.

### **4 DEVICE CHARACTERISTICS**

### 4.1 Device description

Power Bipolar, Power MOSFET technology.

### 4.2 Construction note

### D.U.T.: MJD3055T4 LINE: BA19 PACKAGE: DPAK

| Wafer/Die fab. Information       |                          |  |

|----------------------------------|--------------------------|--|

| Wafer fab manufacturing location | Singapore                |  |

| Technology                       | Planar NPN Power BIPOLAR |  |

| Die finishing back side          | AuAs/Cr/Ni/Au            |  |

| Die size                         | 2240x1940 um             |  |

| Metal                            | Al/Si                    |  |

| Passivation type                 | P-Vapox                  |  |

| Wafer Testing (EWS) information           |           |  |

|-------------------------------------------|-----------|--|

| Electrical testing manufacturing location | Singapore |  |

| Test program                              | WPIS      |  |

| Assembly information                |                                     |  |

|-------------------------------------|-------------------------------------|--|

| Assembly site                       | LONGGANG (China)                    |  |

| Package description                 | DPAK                                |  |

| Molding compound                    | HF Epoxy Resin                      |  |

| Frame material                      | Raw Copper - Frame coating Ni/NiP   |  |

| Die attach process                  | Soft Solder                         |  |

| Die attach material                 | Pb/Sn/Ag                            |  |

| Wire bonding process                | Ultrasonic                          |  |

| Wires bonding materials             | 7 mils Al Base – 10 mils Al Emitter |  |

| Lead finishing/bump solder material | Pure Tin                            |  |

| Final testing information |                  |

|---------------------------|------------------|

| Testing location          | LONGGANG (China) |

| Tester                    | IP TEST          |

### D.U.T.: MJD45H11T4 LINE: B653 PACKAGE: DPAK

| Wafer/Die fab. Information       |                          |  |

|----------------------------------|--------------------------|--|

| Wafer fab manufacturing location | Singapore                |  |

| Technology                       | Planar PNP Power BIPOLAR |  |

| Die finishing back side          | Ti/Ni/Au                 |  |

| Die size                         | 2670x2660 um             |  |

| Metal                            | Al/Si                    |  |

| Passivation type                 | P-Vapox                  |  |

| Wafer Testing (EWS) information           |           |  |

|-------------------------------------------|-----------|--|

| Electrical testing manufacturing location | Singapore |  |

| Test program                              | WPIS      |  |

| Assembly information                |                                          |  |

|-------------------------------------|------------------------------------------|--|

| Assembly site                       | Shenzhen (China)                         |  |

| Package description                 | DPAK                                     |  |

| Molding compound                    | HF Epoxy Resin                           |  |

| Frame material                      | Raw Copper - Frame coating Ni/NiP        |  |

| Die attach process                  | Soft Solder                              |  |

| Die attach material                 | Pb/Sn/Ag                                 |  |

| Wire bonding process                | Ultrasonic                               |  |

| Wires bonding materials             | 7 mils Al-Mg Base – 7 mils Al-Mg Emitter |  |

| Lead finishing/bump solder material | Pure Tin                                 |  |

| Final testing information |                  |

|---------------------------|------------------|

| Testing location          | Shenzhen (China) |

| Tester                    | IP TEST          |

### D.U.T.: STD100NH02LT4 LINE: 3L2S PACKAGE: DPAK

| Wafer/Die fab. Information       |                                  |  |

|----------------------------------|----------------------------------|--|

| Wafer fab manufacturing location | Catania (ITALY)                  |  |

| Technology                       | Power MOSFET STripFET Technology |  |

| Die finishing back side          | Ti/NiV/Au                        |  |

| Die size                         | 3500x2990 um                     |  |

| Metal                            | AlSiCu                           |  |

| Passivation type                 | None                             |  |

| Wafer Testing (EWS) information           |                 |  |

|-------------------------------------------|-----------------|--|

| Electrical testing manufacturing location | Catania (ITALY) |  |

| Test program                              | WPIS            |  |

| Assembly information                |                                         |  |

|-------------------------------------|-----------------------------------------|--|

| Assembly site                       | Shenzhen (China)                        |  |

| Package description                 | DPAK                                    |  |

| Molding compound                    | HF Epoxy Resin                          |  |

| Frame material                      | Raw Copper - Selected Ni/NiP            |  |

| Die attach process                  | Soft Solder                             |  |

| Die attach material                 | Pb/Sn/Ag D.76 mm SSD                    |  |

| Wire bonding process                | Ultrasonic                              |  |

| Wires bonding materials             | 15 mils Al Source and 5 mils Al/Mg Gate |  |

| Lead finishing/bump solder material | 100% Sn                                 |  |

| Final testing information |                  |  |

|---------------------------|------------------|--|

| Testing location          | Shenzhen (China) |  |

| Tester                    | IP TEST          |  |

### D.U.T.: STD20NF06LT4 LINE: EL6C PACKAGE: DPAK

| Wafer/Die fab. Information       |                                  |  |

|----------------------------------|----------------------------------|--|

| Wafer fab manufacturing location | Catania (ITALY)                  |  |

| Technology                       | Power MOSFET STripFET Technology |  |

| Die finishing back side          | Ti-Ni-Au                         |  |

| Die size                         | 2550x1950 um                     |  |

| Metal                            | Al/Si                            |  |

| Passivation type                 | None                             |  |

| Wafer Testing (EWS) information           |                 |  |

|-------------------------------------------|-----------------|--|

| Electrical testing manufacturing location | Catania (ITALY) |  |

| Test program                              | WPIS            |  |

| Assembly information                |                                               |

|-------------------------------------|-----------------------------------------------|

| Assembly site                       | LONGGANG (China)                              |

| Package description                 | DPAK                                          |

| Molding compound                    | HF Epoxy Resin                                |

| Frame material                      | Raw Copper - Frame coating Ni/NiP             |

| Die attach process                  | Soft Solder                                   |

| Die attach material                 | Pb/Ag/Sn                                      |

| Wire bonding process                | Ultrasonic                                    |

| Wires bonding materials             | 5 mils Al/Mg Gate Pad – 10 mils Al Source Pad |

| Lead finishing/bump solder material | Pure Tin                                      |

| Final testing information |                  |

|---------------------------|------------------|

| Testing location          | LONGGANG (China) |

| Tester                    | IP TEST          |

# D.U.T.: STD2HNK60Z LINE: EZ60 PACKAGE: DPAK

| Wafer/Die fab. information       |                                   |

|----------------------------------|-----------------------------------|

| Wafer fab manufacturing location | Singapore                         |

| Technology                       | Power MOSFET SuperMESH Technology |

| Die finishing back side          | Ti-Ni-Au                          |

| Die size                         | 2410x2000 um                      |

| Metal                            | Al/Si                             |

| Passivation type                 | Nitride                           |

| Wafer Testing (EWS) information           |           |

|-------------------------------------------|-----------|

| Electrical testing manufacturing location | Singapore |

| Test program                              | WPIS      |

| Assembly information                |                          |  |

|-------------------------------------|--------------------------|--|

| Assembly site                       | Shenzhen (China)         |  |

| Package description                 | DPAK                     |  |

| Molding compound                    | HF Epoxy Resin           |  |

| Frame material                      | Raw Copper - selected Ni |  |

| Die attach process                  | Soft Solder              |  |

| Die attach material                 | Pb/Ag/Sn                 |  |

| Wire bonding process                | Termosonic               |  |

| Wires bonding materials             | Al                       |  |

| Lead finishing/bump solder material | Pure Tin                 |  |

| Final testing information |                  |

|---------------------------|------------------|

| Testing location          | Shenzhen (China) |

| Tester                    | IP TEST          |

#### D.U.T.: STD4NK60ZT4 LINE: EZ62 PACKAGE: DPAK

| Wafer/Die fab. information       |                                   |

|----------------------------------|-----------------------------------|

| Wafer fab manufacturing location | Catania (ITALY)                   |

| Technology                       | Power MOSFET SuperMESH Technology |

| Die finishing back side          | Ti-Ni-Au                          |

| Die size                         | 3180x2650 um                      |

| Metal                            | Al/Si                             |

| Passivation type                 | Nitride                           |

| Wafer Testing (EWS) information           |                 |

|-------------------------------------------|-----------------|

| Electrical testing manufacturing location | Catania (ITALY) |

| Test program                              | WPIS            |

| Assembly information                |                                        |

|-------------------------------------|----------------------------------------|

| Assembly site                       | LONGGANG (China)                       |

| Package description                 | DPAK                                   |

| Molding compound                    | HF Epoxy Resin                         |

| Frame material                      | Raw Copper - Frame coating selected Ni |

| Die attach process                  | Soft Solder                            |

| Die attach material                 | Pb/Ag/Sn                               |

| Wire bonding process                | Termosonic                             |

| Wires bonding materials             | 2 mils Cu                              |

| Lead finishing/bump solder material | Pure Tin                               |

| Final testing information |                  |

|---------------------------|------------------|

| Testing location          | LONGGANG (China) |

| Tester                    | IP TEST          |