# VND5004ASP30-E (VH01)

# Package MultiPowerSO30 New frame for sagging wire improvement

|      | Revision history               |                              |                     |  |  |  |  |  |  |

|------|--------------------------------|------------------------------|---------------------|--|--|--|--|--|--|

| Rev. | Date of Release                | Author                       | Changes description |  |  |  |  |  |  |

| 0.1  | September 4 <sup>th</sup> 2014 | F. Ceraulo - APG Q&R Catania | Creation            |  |  |  |  |  |  |

RR002714CT2235 Page: 1 of 10

|         | Table of contents |                                                            |  |  |  |  |  |

|---------|-------------------|------------------------------------------------------------|--|--|--|--|--|

| Section | Pag               | Content                                                    |  |  |  |  |  |

| 1       | 3                 | Reliability evaluations overview                           |  |  |  |  |  |

| 1.1     | 3                 | Objectives                                                 |  |  |  |  |  |

| 1.2     | 3                 | Results                                                    |  |  |  |  |  |

| 2       | 4                 | Traceability                                               |  |  |  |  |  |

| 3       | 5                 | Devices characteristics                                    |  |  |  |  |  |

| 3.1     | 5                 | Generalities                                               |  |  |  |  |  |

| 3.2     | 6                 | Pins connection                                            |  |  |  |  |  |

| 3.3     | 6                 | Blocks diagram                                             |  |  |  |  |  |

| 4       | 7                 | Reliability qualification plan and results – Summary table |  |  |  |  |  |

RR002714CT2235 Page: 2 of 10

# - 1. Reliability evaluations overview

#### 1.1 Objectives

Aim of this report is to present the results of the reliability evaluations performed on **VND5004ASP30-E** (VH01 as ST internal code) chosen as test vehicle to release in production a new frame for package MultiPowerSO30.

This product is a 4mohm Dual Channel High Side Driver with analog current sense for Automotive Applications designed in VIPower M05 technology, composed by two power dice (VNI4 as ST internal silicon line) and one signal die (VNG4 as ST internal silicon line) both diffused in ST AMK6 Ang Mo Kio (Singapore) 6" wafer fab.

The new frame is introduced for sagging wire improvement and was designed to make the floating paddle more rigid reducing the vertical vibration during handling.

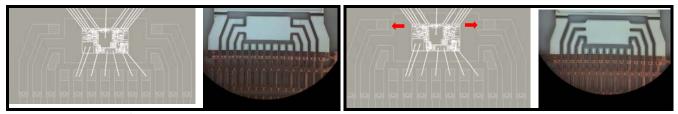

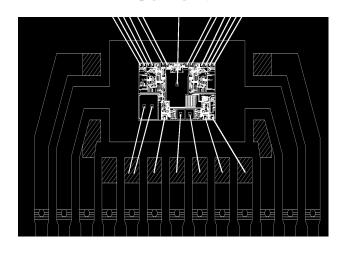

Current frame New frame

Change between the current and the new frames occurs only in a geometry dimension (see red arrows for details) but not in the material or in the assembly configuration.

The qualification was done according to **AEC\_Q100 Rev.G** specification following the path described here below:

| Te | st group as per AEC-Q100 Rev.G  | Performed (Y/N) | Comment                               |

|----|---------------------------------|-----------------|---------------------------------------|

| Α  | Accelerated Environment Stress  | Y               |                                       |

| В  | Accelerated Lifetime Simulation | N               | Not applicable                        |

| С  | Package Assembly Integrity      | Y               |                                       |

| D  | Die Fabrication Reliability     | N               | Not applicable                        |

| Е  | Electrical Verification         | N               | Not applicable                        |

| F  | Defect Screening                | N               | Not applicable                        |

| G  | Cavity Package Integrity        | N               | N/A: not for plastic packaged devices |

See details per each test group in section 4 of this report.

In the below table a comparison between the AEC-Q100 and ZVEI requirements for this kind of change (lead frame dimension) vs the applied ST qualification plan is reported:

RR002714CT2235 Page: 3 of 10

#### **Automotive Product Group**

Quality and Reliability Reliability Report

|          |     | Tes | t Grou | рA  |      | Test G | roup B |     | Test G | roup C |    |    | Tes  | t Grou | p D  |    |     |     | Tes | t Grou | рE |     |    |

|----------|-----|-----|--------|-----|------|--------|--------|-----|--------|--------|----|----|------|--------|------|----|-----|-----|-----|--------|----|-----|----|

|          | тнв | AC  | тс     | РТС | HTSL | HTOL   | ELFR   | WBS | WBP    | SD     | PD | EM | TDDB | нсі    | NBTI | SM | нвм | СДМ | LU  | ED     | GL | ЕМС | sc |

| AEC-Q100 |     | x   | ×      | ×   |      |        |        |     |        | x      | x  |    |      |        |      |    |     |     |     |        |    |     | x  |

| ZVEI     |     | x   | x      | x   |      |        |        |     |        | x      | x  |    |      |        |      |    |     |     |     |        |    |     | х  |

| ST       |     | х   | х      |     |      |        |        | x   | x      | x      | x  |    |      |        |      |    |     |     |     |        |    |     |    |

The applied qualification plan was addressed to investigate about failure mechanisms related to the thermo mechanical and humidity stress while the impact of the change is considered negligible vs the failure mechanism related to PTC and SC (no change in wires/assembly configuration/die attach).

#### 1.2 Results

All reliability tests have been completed with positive results neither functional nor parametric rejects were detected at final electrical testing.

The Package Assembly Integrity (test Group C) pointed out neither abnormal break loads nor forbidden failure modes.

Based on the overall positive results we consider the products qualified from a reliability point of view.

### - 2. Traceability

| Wafer fab information            |                                                                                                               |  |  |  |  |  |

|----------------------------------|---------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Wafer fab manufacturing location | ST AMK6 Ang Mo Kio (Singapore)                                                                                |  |  |  |  |  |

| Wafer diameter (inches)          | 6                                                                                                             |  |  |  |  |  |

| Silicon process technology       | VIPower M05                                                                                                   |  |  |  |  |  |

| Die finishing back side          | Ti-Ni-Au                                                                                                      |  |  |  |  |  |

| Die size (micron)                | VNG4 (signal): 2800 x 1560<br>VNI4 (power): 7990 x 4000                                                       |  |  |  |  |  |

| Metal levels / materials         | VNG4 (signal): 2 levels / Ti/TiN/Ti/AlSiCu (3.2 μm last level)<br>VNI4 (power) : 1 level / Ti/AlSiCu (4.5 μm) |  |  |  |  |  |

| Die finishing front side         | SiN/POLYIMIDE                                                                                                 |  |  |  |  |  |

| Diffusion Lots #                 | VNG4 (signal): 61431X3, VNI4 (power): 63245T5                                                                 |  |  |  |  |  |

| Assembly Information              |                                                |  |  |  |  |  |

|-----------------------------------|------------------------------------------------|--|--|--|--|--|

| Assembly plant location           | ST Muar (Malaysia)                             |  |  |  |  |  |

| Package description               | Multi PowerSO_30                               |  |  |  |  |  |

| Molding compound                  | RESIN SUMITOMO EME-G600C                       |  |  |  |  |  |

| Wires bonding materials/diameters | Au 1.2mils (on signal) / Al 15mils (on power)  |  |  |  |  |  |

| Die attach material               | GLUE QMI9507                                   |  |  |  |  |  |

|                                   | PREFORM Pb/Ag/Sn 97.5/1.5/1                    |  |  |  |  |  |

| Assembly Lots #                   | 993360NR01 (old frame), 993360NR02 (new frame) |  |  |  |  |  |

| Reliability Information             |                    |  |  |  |  |

|-------------------------------------|--------------------|--|--|--|--|

| Reliability test execution location | ST Catania (Italy) |  |  |  |  |

RR002714CT2235 Page: 4 of 10

Reliability Report

#### - 3. Device characteristics

#### 3.1 Generalities

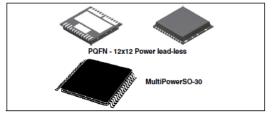

## VND5004A-E VND5004ASP30-E

Double  $4m\Omega$  high side driver with analog current sense for automotive applications

#### **Features**

| Max transient supply voltage      | V <sub>CC</sub>   | 41V                 |

|-----------------------------------|-------------------|---------------------|

| Operating voltage range           | V <sub>CC</sub>   | 4.5 to 27V          |

| Max On-State resistance (per ch.) | R <sub>ON</sub>   | 4 mΩ                |

| Current limitation (typ)          | I <sub>LIMH</sub> | 100A                |

| Off state supply current          | Is                | 2 μA <sup>(1)</sup> |

1. Typical value with all loads connected

#### General

- Inrush current active management by power limitation

- Very low stand-by current

- 3.0V CMOS compatible input

- Optimized electromagnetic emission

- Very low electromagnetic susceptibility

- In compliance with the 2002/95/EC European directive

- Diagnostic functions

- Proportional load current sense

- Current sense disable

- Thermal shutdown indication

#### Protection

- Undervoltage shut-down

- Overvoltage clamp

- Load current limitation

- Thermal shut down

- Self limiting of fast thermal transients

- Protection against loss of ground and loss of V<sub>CC</sub>

- Reverse battery protection with self switch on of the PowerMOS (see Application schematic on page 18)

- Electrostatic discharge protection

#### **Application**

- All types of resistive, inductive and capacitive loads

- Suitable for power management applications

#### Description

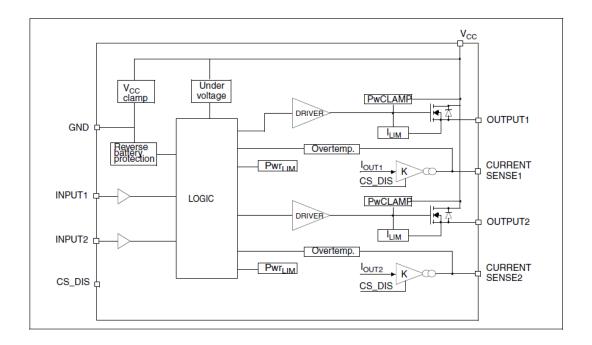

The VND5004ATR-E and VND5004ASP30-E are devices made using STMicroelectronics VIPower technology. They are intended for driving resistive or inductive loads with one side connected to ground. Active V<sub>CC</sub> pin voltage clamp and load dump protection circuit protect the devices against transients on the Vcc pin (see ISO7637 transient compatibility table). These devices integrate an analog current sense which delivers a current proportional to the load current (according to a known ratio) when CS\_DIS is driven low or left open. When CS\_DIS is driven high, the CURRENT SENSE pin is high impedance. Output current limitation protects the devices in overload condition. In case of long duration overload, the devicesa limit the dissipated power to a safe level up to thermal shut-down intervention. Thermal shut-down with automatic restart allows the device to recover normal operation as soon as a fault condition disappears.

Table 1. Devices summary

| Table 1. Devices summary   |                |                  |            |  |  |  |  |

|----------------------------|----------------|------------------|------------|--|--|--|--|

| Package                    | Order codes    |                  |            |  |  |  |  |

| 1 dekage                   | Tube           | Tape and Reel    | Tray       |  |  |  |  |

| PQFN-12x12 Power lead-less | -              | VND5004ATR-E     | VND5004A-E |  |  |  |  |

| MultiPowerSO-30            | VND5004ASP30-E | VND5004ASP30TR-E | -          |  |  |  |  |

RR002714CT2235 Page: 5 of 10

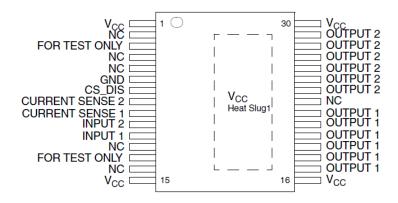

#### 3.2 Pins connection

#### 3.3 Blocks diagram

RR002714CT2235 Page: 6 of 10

# - 4. Reliability qualification plan and results

|          | Test group A: Accelerated Environment Stress |                                                                                                                                                                                           |                      |                          |                                    |  |  |  |  |  |

|----------|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--------------------------|------------------------------------|--|--|--|--|--|

| AEC<br># | Test Name                                    | STM Test Conditions                                                                                                                                                                       | Sample Size/<br>Lots | Results<br>Fails/SS/Lots | Comments                           |  |  |  |  |  |

| A1       | PC<br>Pre Cond                               | - Preconditioning according to Jedec JESD22-A113F including 5 Temperature Cycling Ta=-40°C/+60°C - Reflow according to level 3 Jedec JSTD020D-1 - 100 Temperature Cycling Ta=-50°C/+150°C | Before AC, TC        |                          |                                    |  |  |  |  |  |

| A2       | THB Temp Humidity Bias                       | Ta=85°C, RH=85%, Vcc=24V for 1000 hours                                                                                                                                                   | -                    | -                        | Not Applicable                     |  |  |  |  |  |

| А3       | AC<br>Autoclave                              | TC (Ta=-65°C / +150°C for 100 cycles) + AC (Ta=121°C, Pa=2atm for 96 hours)                                                                                                               | 77/2                 | 0/77/2                   | 1 Lot old frame<br>1 Lot new frame |  |  |  |  |  |

| A4       | TC<br>Temp.<br>Cycling                       | Ta=-65°C / +150°C for 500 cycles                                                                                                                                                          | 77/2                 | 0/77/2                   | 1 Lot old frame<br>1 Lot new frame |  |  |  |  |  |

| A5_      | PTC Power Temp. Cycling                      | Ta=-40°C / +125°C for 1000 cycles.                                                                                                                                                        | -                    | -                        | Not Applicable                     |  |  |  |  |  |

| A6       | HTSL<br>High Temp.<br>Storage Life           | Ta=150°C for 1000 hours.                                                                                                                                                                  | -                    | -                        | Not Applicable                     |  |  |  |  |  |

|          | Test group A: Accelerated Environment Stress Robustness activity |                                   |                      |                          |                                    |  |  |  |  |  |

|----------|------------------------------------------------------------------|-----------------------------------|----------------------|--------------------------|------------------------------------|--|--|--|--|--|

| AEC<br># | Test<br>Name                                                     | STM Test Conditions               | Sample<br>Size/ Lots | Results<br>Fails/SS/Lots | Comments                           |  |  |  |  |  |

| A4       | TC<br>Temp.<br>Cycling                                           | Ta=-50°C / +150°C for 1000 cycles | 77/2                 | 0/77/2                   | 1 Lot old frame<br>1 Lot new frame |  |  |  |  |  |

RR002714CT2235 Page: 7 of 10

|          | Test group B: Accelerated Lifetime Simulation |                                                                                         |                      |                          |                |  |  |  |  |

|----------|-----------------------------------------------|-----------------------------------------------------------------------------------------|----------------------|--------------------------|----------------|--|--|--|--|

| AEC<br># | Test Name                                     | STM Test Conditions                                                                     | Sample Size/<br>Lots | Results<br>Fails/SS/Lots | Comments       |  |  |  |  |

| B1       | HTOL<br>High Temp.<br>Op. Life                | Bias Static stress (JESD22-A108):<br><b>HTB</b> Tamb=125°C, Vcc=28V for<br>1000 hours   | -                    | -                        | Not Applicable |  |  |  |  |

| B2       | ELFR<br>Early Life<br>Failure Rate            | Parts submitted to <b>HTOL</b> per JESD22-A108 requirements; GRADE 1: 24 hours at 150°C | -                    | -                        | Not Applicable |  |  |  |  |

| В3       | EDR<br>Endurance<br>Data<br>Retention         | Only for memory devices                                                                 | -                    | -                        | Not Applicable |  |  |  |  |

| Test group C: Package Assembly Integrity |                              |                                        |                                       |                                             |                                    |  |

|------------------------------------------|------------------------------|----------------------------------------|---------------------------------------|---------------------------------------------|------------------------------------|--|

| AEC<br>#                                 | Test Name                    | STM Test Conditions                    | Sample Size/<br>Lots                  | Results<br>Fails/SS/Lots                    | Comments                           |  |

| C1                                       | WBS<br>Wire Bond<br>Shear    |                                        | 30 bonds<br>/minimum 5<br>units/1 lot | All<br>measurement<br>within spec<br>limits | 1 Lot old frame<br>1 Lot new frame |  |

| <b>C2</b>                                | WBP<br>Wire Bond<br>Pull     |                                        | 30 bonds<br>/minimum 5<br>units/1 lot | All<br>measurement<br>within spec<br>limits | 1 Lot old frame<br>1 Lot new frame |  |

| <b>C3</b>                                | <b>SD</b><br>Solderability   |                                        | 15/4                                  | Passed                                      | 1 Lot old frame<br>1 Lot new frame |  |

| <b>C4</b>                                | PD<br>Physical<br>Dimensions |                                        | 10/4                                  | Passed                                      | 1 Lot old frame<br>1 Lot new frame |  |

| C5                                       | SBS<br>Solder Ball<br>Shear  | Only for BGA package                   | -                                     | -                                           | Not Applicable                     |  |

| <b>C6</b>                                | LI<br>Lead<br>Integrity      | Not required for Surface Mount Devices | -                                     | -                                           | Not Applicable                     |  |

RR002714CT2235 Page: 8 of 10

| Test group D: Die Fabrication Reliability |                                            |                     |                      |                          |                |  |

|-------------------------------------------|--------------------------------------------|---------------------|----------------------|--------------------------|----------------|--|

| AEC<br>#                                  | Test Name                                  | STM Test Conditions | Sample Size/<br>Lots | Results<br>Fails/SS/Lots | Comments       |  |

| D1                                        | <b>EM</b><br>Electromigration              |                     | -                    | -                        | Not Applicable |  |

| D2                                        | TDDB Time Dependent Dielectric Breakdown   |                     | -                    | -                        | Not Applicable |  |

| D3                                        | HCI<br>Hot Carrier<br>Injection            |                     | -                    | -                        | Not Applicable |  |

|                                           | NBTI Negative Bias Temperature Instability |                     | -                    | -                        | Not Applicable |  |

| D5                                        | SM<br>Stress Migration                     |                     | -                    | -                        | Not Applicable |  |

|            | Test group E: Electrical Verification   |                     |                      |                          |                |  |  |

|------------|-----------------------------------------|---------------------|----------------------|--------------------------|----------------|--|--|

| AEC<br>#   | Test Name                               | STM Test Conditions | Sample<br>Size/ Lots | Results<br>Fails/SS/Lots | Comments       |  |  |

| E2         | ESD<br>HBM / MM                         |                     | -                    | -                        | Not Applicable |  |  |

| E3         | ESD<br>CDM                              |                     | -                    | -                        | Not Applicable |  |  |

| E4         | <b>LU</b><br>Latch-Up                   |                     | -                    | -                        | Not Applicable |  |  |

| <b>E</b> 5 | ED<br>Electrical<br>Distributions       |                     | -                    | -                        | Not Applicable |  |  |

| <b>E7</b>  | CHAR<br>Characterization                |                     | -                    | -                        | Not Applicable |  |  |

| E8         | GL<br>Gate Leakage                      |                     | -                    | -                        | Not Applicable |  |  |

| <b>E9</b>  | EMC<br>Electromagnetic<br>Compatibility |                     | -                    | -                        | Not Applicable |  |  |

RR002714CT2235 Page: 9 of 10

Automotive Product Group

Quality and Reliability

Reliability Report

| E10 | SC<br>Short Circuit<br>Characterization | According to AEC-Q100-012 | - | Not Applicable |

|-----|-----------------------------------------|---------------------------|---|----------------|

|-----|-----------------------------------------|---------------------------|---|----------------|

| Test group F: Defects Screening Tests |                                             |                     |                      |                          |          |  |

|---------------------------------------|---------------------------------------------|---------------------|----------------------|--------------------------|----------|--|

| AEC<br>#                              | Test Name                                   | STM Test Conditions | Sample<br>Size/ Lots | Results<br>Fails/SS/Lots | Comments |  |

| F1                                    | PAT Process Average Testing                 |                     | Not Applicable       |                          |          |  |

| F2                                    | SBA<br>Statistical<br>Bin/Yield<br>Analysis |                     |                      |                          |          |  |

| Test group G: Cavity Package Integrity Tests |                                  |                                                  |                      |                          |          |  |  |

|----------------------------------------------|----------------------------------|--------------------------------------------------|----------------------|--------------------------|----------|--|--|

| AEC<br>#                                     | Test Name                        | STM Test Conditions                              | Sample<br>Size/ Lots | Results<br>Fails/SS/Lots | Comments |  |  |

| G1                                           | MS<br>Mechanical<br>Shock        |                                                  |                      |                          |          |  |  |

| G2                                           | VFV Variable Frequency Vibration |                                                  |                      |                          |          |  |  |

| <b>G</b> 3                                   | CA<br>Constant<br>Acceleration   |                                                  |                      |                          |          |  |  |

| <b>G</b> 4                                   | <b>GFL</b><br>Gross/Fine Leak    |                                                  |                      |                          |          |  |  |

| G5                                           | <b>DROP</b><br>Package Drop      | Not applicable: not for plastic packaged devices |                      |                          |          |  |  |

| G6                                           | <b>LT</b><br>Lid Torque          |                                                  |                      |                          |          |  |  |

| <b>G7</b>                                    | <b>DS</b><br>Die Shear           |                                                  |                      |                          |          |  |  |

| <b>G8</b>                                    | IWV<br>Internal Water<br>Vapor   |                                                  |                      |                          |          |  |  |

Page: 10 of 10 RR002714CT2235

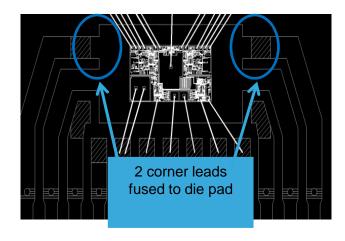

# VIPower housed in PowerSO-30: Wire Sagging Improvement

#### WHAT:

In order to improve quality a modification of lead frame has been implemented. Corner leads are fused together in order to improve wire sagging and to avoid pad tilt/movement during handling

#### WHY:

**Quality Improvement**

#### HOW:

See enclosed description of the change and qualification report RR002714CT2235

#### HOW:

Change will be implemented according the following schedule

Samples: Available on demand

Qualification results: enclosed to this communication

Implementation: May 2015, but we are ready to implement the change prior this date

upon Customer agreement

# VIPower housed in PowerSO-30: Wire Sagging Improvement

#### Current

No corner leads are fused together in

#### New

Corner leads are fused together in order to improve wire sagging and to avoid pad tilt/movement during handling