## PRODUCT / PROCESS CHANGE NOTIFICATION

|                      | 1. PCN basic data |                                                                          |

|----------------------|-------------------|--------------------------------------------------------------------------|

| 1.1 Company          | <b>577</b>        | STMicroelectronics International N.V                                     |

| 1.2 PCN No.          |                   | AMS/20/12144                                                             |

| 1.3 Title of PCN     |                   | New assembly site for General Purpose Analog products in MiniSO8 package |

| 1.4 Product Category | 1                 | See product list                                                         |

| 1.5 Issue date       |                   | 2020-05-14                                                               |

|                           | 2. PCN Team                            |

|---------------------------|----------------------------------------|

| 2.1 Contact supplier      |                                        |

| 2.1.1 Name                | NEMETH KRISZTINA                       |

| 2.1.2 Phone               | +49 89460062210                        |

| 2.1.3 Email               | krisztina.nemeth@st.com                |

| 2.2 Change responsibility |                                        |

| 2.2.1 Product Manager     | Domenico ARRIGO,Marcello SAN BIAGIO    |

| 2.1.2 Marketing Manager   | Fulvio PULICELLI,Salvatore DI VINCENZO |

| 2.1.3 Quality Manager     | Alessandro PLATINI, Jean-Marc BUGNARD  |

|              | 3. Change                                                                                                                                             |                            |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| 3.1 Category | 3.2 Type of change                                                                                                                                    | 3.3 Manufacturing Location |

| Transfer     | Line transfer for a full process or process brick<br>(process step, control plan, recipes) from one<br>site to another site: Assembly site (SOP 2617) |                            |

|                                                                                       | 4. Description of c                                    | hange                                                               |  |

|---------------------------------------------------------------------------------------|--------------------------------------------------------|---------------------------------------------------------------------|--|

|                                                                                       | Old                                                    | New                                                                 |  |

| 4.1 Description                                                                       | Assembly plant : - Amkor Philippines - Carsem Malaysia | Assembly plant : - TSHT China - Amkor Philippines - Carsem Malaysia |  |

| 4.2 Anticipated Impact on form,fit, function, quality, reliability or processability? | No impact                                              |                                                                     |  |

|                      | 5. Reason / motivation for change                                                                                                                                                                                                                                              |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.1 Motivation       | The purpose of the introduction of TSHT for both Assy and Test & Finishing activities is to further improve the rationalization of our manufacturing assets and provide a better support to our customers by enhancing the manufacturing process for higher volume production. |

| 5.2 Customer Benefit | SERVICE IMPROVEMENT                                                                                                                                                                                                                                                            |

|                 | 6. Marking of parts / traceability of change |

|-----------------|----------------------------------------------|

| 6.1 Description | New Finished good codes                      |

|                                     | 7. Timing / schedule |  |

|-------------------------------------|----------------------|--|

| 7.1 Date of qualification results   | 2020-04-30           |  |

| 7.2 Intended start of delivery      | 2020-08-15           |  |

| 7.3 Qualification sample available? | Upon Request         |  |

|                                                    | 8. Qualification / Validation      |               |            |

|----------------------------------------------------|------------------------------------|---------------|------------|

| 8.1 Description                                    | 12144 PCN standard-MiniSO TSHT.pdf |               |            |

| 8.2 Qualification report and qualification results | Available (see attachment)         | Issue<br>Date | 2020-05-14 |

## 9. Attachments (additional documentations)

12144 Public product.pdf 12144 PCN standard-MiniSO TSHT.pdf

|                         | 10. Affected part       | s                        |

|-------------------------|-------------------------|--------------------------|

|                         | 10. 1 Current           | 10.2 New (if applicable) |

| 10.1.1 Customer Part No | 10.1.2 Supplier Part No | 10.1.2 Supplier Part No  |

|                         | LM358ST                 |                          |

| TS462CST                | TS462CST                |                          |

|                         | TSV358IST               |                          |

## **IMPORTANT NOTICE - PLEASE READ CAREFULLY**

Subject to any contractual arrangement in force with you or to any industry standard implemented by us, STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2018 STMicroelectronics - All rights reserved

# **Public Products List**

Publict Products are off the shelf products. They are not dedicated to specific customers, they are available through ST Sales team, or Distributors, and visible on ST.com

PCN Title: New assembly site for General Purpose Analog products in MiniSO8 package

PCN Reference: AMS/20/12144

Subject: Public Products List

Dear Customer,

Please find below the Standard Public Products List impacted by the change.

| LMV822IST  | TSV992AIST | TSV6192AIST |

|------------|------------|-------------|

| TSV632AIST | TSV992IST  | LMV358LIST  |

| LM358ST    | TSV612IST  | TSV622AIST  |

| TS462CST   | TS332IST   | TS1852AIST  |

| LM2904ST   | LMV822AIST | TS1872AIST  |

| TSV612AIST | LM293ST    | TSV912AIST  |

| TSV912IST  | TS3022IST  | LMV393IST   |

| LM358AWST  | LM393ST    | LMX358IST   |

| TS972IST   | TS1852IST  | TSV6392AIST |

| PM8834MTR  | TSV358IST  | LM358WST    |

| LM2903ST   | TSV632IST  | TSV6292AIST |

| LM258AST   |            |             |

#### **IMPORTANT NOTICE - PLEASE READ CAREFULLY**

Subject to any contractual arrangement in force with you or to any industry standard implemented by us, STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2018 STMicroelectronics - All rights reserved

# PRODUCT/PROCESS

**CHANGE NOTIFICATION**

PCN AMS/20/12144

# Analog, MEMS & Sensors (AMS)

New assembly site for General Purpose Analog products in MiniSO8 packages

April 2020 5

#### WHAT:

Progressing on activities related to process modernization and quality improvement, ST is pleased to announce the introduction of TSHT/China as an added subcontractor for Assy and Test & Finishing activities for some products assembled in our MiniSO8 package.

Please find more information related to material change in the table here below

| Material           | Current process                               | Modified process                              | Comment |

|--------------------|-----------------------------------------------|-----------------------------------------------|---------|

| Diffusion location | ST Ang Mo Kio (Singapore)/<br>UMC / ST Agrate | ST Ang Mo Kio (Singapore)/ UMC / ST<br>Agrate |         |

| Assembly location  | Amkor Philippines<br>Carsem Malaysia          | TSHT China                                    |         |

| Molding compound   | Sumitomo G700<br>Hitachi CEL 8240             | Hitachi CEL 9220                              |         |

| Die attach         | Henkel 8290 / QMI519                          | Henkel 8200T/Henkel8600                       |         |

| Leadframe          | Copper                                        | Copper                                        |         |

| Plating            | NiPdAu / Matte Sn                             | Matte Sn                                      |         |

| Wire               | Gold 1.2Mils/1mil / 0.8Mil                    | Gold 1.3mils / Copper Pd coated 1 mil         |         |

#### WHY:

The purpose of the introduction of TSHT for both Assy and Test & Finishing activities for the here above listed commercial products is to further improve the rationalization of our manufacturing assets and provide a better support to our customers by enhancing the manufacturing process for higher volume production.

## HOW:

The qualification program consists mainly of comparative electrical characterization and reliability tests.

You will find here after the qualification test plan which summarizes the various test methods and conditions that ST uses for this qualification program.

### WHEN:

The new material set will be implemented in Q2/2020 in TSHT China.

## Marking and traceability:

Unless otherwise stated by customer's specific requirement, the traceability of the parts assembled with the new material set will be ensured by new internal sales type, date code and lot number.

The changes here reported will not affect the electrical, dimensional and thermal parameters keeping unchanged all the information reported on the relevant datasheets.

There is -as well- no change in the packing process or in the standard delivery quantities. Shipments may start earlier with the customer's written agreement.

# Reliability Qualification plan

AMS Back-end qualification MSOP 8

Production transfer to TSHT

**General Information**

**Product Line** 0193, 0358, V992, UY36, UQ18

Dual comparator bipolar, Dual op amp bipolar, , Dual op amp,

Product Description biCMOS, Dual precision op

amp, 4 A dual low-side

MOSFET driver

$LM2903WST,\,LM2904WST,$

TSV992IST, TSX7192IST,

PM8834

**Product Group**AMS

P/N

Product division General Purpose Analog &RF

Package MiniSO8, MiniSO8 exposed pad

Silicon Process technology Bipolar, HF5CMOS, HVG8A

|                 | Locations |                                |

|-----------------|-----------|--------------------------------|

| Wafer fab       |           | ST Singapore<br>UMC, ST Agrate |

| Waler ras       |           | one, si ngrave                 |

| Assembly plant  |           | TSHT China                     |

| , F-3440        |           |                                |

| Reliability Lab |           | ST Grenoble,<br>TSHT           |

|                 |           |                                |

|                 |           |                                |

|                 |           |                                |

|                 |           |                                |

Note: This report is a summary of the reliability trials performed in good faith by STMicroelectronics in order to evaluate the potential reliability risks during the product life using a set of defined test methods.

This report does not imply for STMicroelectronics expressly or implicitly any contractual obligations other than as set forth in STMicroelectronics general terms and conditions of Sale. This report and its contents shall not be disclosed to a third party without previous written agreement from STMicroelectronics.

# TABLE OF CONTENTS

| 1 | APPI | LICABLE AND REFERENCE DOCUMENTS | 9                            |

|---|------|---------------------------------|------------------------------|

|   |      | SSARY                           |                              |

|   |      | ABILITY EVALUATION OVERVIEW     |                              |

|   | 3.1  | OBJECTIVES                      | 9                            |

|   | 3.2  | CONCLUSION                      | 9                            |

| 4 | DEVI | CE CHARACTERISTICS              |                              |

|   | 4.1  | DEVICE DESCRIPTION              |                              |

|   |      | CONSTRUCTION NOTE               |                              |

| 5 | TEST | TS RESULTS SUMMARY              | 16                           |

|   | 5.1  | TEST VEHICLE                    |                              |

|   |      | TEST PLAN AND RESULTS SUMMARY   |                              |

| 6 | ANN  | EXES                            |                              |

|   | 6.1  | DEVICE DETAILS                  | ERROR! BOOKMARK NOT DEFINED. |

|   | 6.2  | TESTS DESCRIPTION               |                              |

# **1 APPLICABLE AND REFERENCE DOCUMENTS**

| Document reference | Short description                                       |  |  |  |  |

|--------------------|---------------------------------------------------------|--|--|--|--|

| JESD47             | Stress-Test-Driven Qualification of Integrated Circuits |  |  |  |  |

# **2 GLOSSARY**

| DUT Device Under Test     |             |  |  |

|---------------------------|-------------|--|--|

| PCB Printed Circuit Board |             |  |  |

| SS                        | Sample Size |  |  |

|                           |             |  |  |

# **3 RELIABILITY EVALUATION OVERVIEW**

# 3.1 Objectives

To qualify a new assembly site, TSHT China, for products in MiniSO8 package for Analog products.

# 3.2 Conclusion

Qualification Plan requirements have to be fulfilled without issue. It is stressed that reliability tests have to show that the devices behave correctly against environmental tests (no failure). Moreover, the stability of electrical parameters during the accelerated tests have to demonstrate the ruggedness of the products and safe operation, which is consequently expected during their lifetime.

# **4 DEVICE CHARACTERISTICS**

# 4.1 **Device description**

#### LM2903WST

# LM2903W

Low-power, dual-voltage comparator

#### Datasheet - production data

#### **Features**

- Wide, single supply voltage range or dual supplies +2 V to +36 V or ±1 V to ±18 V

- Very low supply current (0.4 mA) independent of supply voltage (1 mW/comparator at +5 V)

- Low input bias current: 25 nA typ.

- Low input offset current: ±5 nA typ.

- Input common-mode voltage range includes negative rail

- Low output saturation voltage: 250 mV typ. (I<sub>O</sub> = 4 mA)

- Differential input voltage range equal to the supply voltage

- TTL, DTL, ECL, MOS, CMOS compatible outputs

- ESD internal protection: 2 kV

## Description

This device consists of two independent lowpower voltage comparators designed specifically to operate from a single supply over a wide range of voltages. Operation from split power supplies is also possible.

The input common-mode voltage range includes negative rail even though operated from a single power supply voltage.

All pins are protected against electrostatic discharge up to 2 kV. Consequently, the input voltages must not exceed the  $V_{CC}^+$  or  $V_{CC}^-$  magnitudes.

#### LM2904WST.

# LM2904, LM2904A LM2904W, LM2904AW

Datasheet

### Low-power dual operational amplifier

#### **Features**

- Frequency compensation implemented internally

- Large DC voltage gain: 100 dB

- Wide bandwidth (unity gain): 1.1 MHz (temperature compensated)

- Very low supply current/amplifier, essentially independent of supply voltage

- Low input bias current: 20 nA (temperature compensated)

- Low input offset current: 2 nA

- Input common-mode voltage range includes negative rail

- Differential input voltage range equal to the power supply voltage

- Large output voltage swing 0 V to [(V<sub>CC</sub> +) -1.5 V]

#### Description

This circuit consists of two independent, high gain operational amplifiers (op amps) that have frequency compensation implemented internally. They are designed specifically for automotive and industrial control systems. The circuit operates from a single power supply over a wide range of voltages. The low power supply drain is independent of the magnitude of the power supply voltage.

Application areas include transducer amplifiers, DC gain blocks and all the conventional op amp circuits which can now be more easily implemented in single power supply systems. For example, these circuits can be directly supplied from the standard 5 V which is used in logic systems and easily provides the required electronic interfaces without requiring any additional power supply.

In linear mode, the input common-mode voltage range includes ground and the output voltage can also swing to ground, even though operated from a single power supply.

| Maturity status link |                             |                 |  |  |  |  |  |  |

|----------------------|-----------------------------|-----------------|--|--|--|--|--|--|

|                      | Enhanced<br>V <sub>IO</sub> | Enhanced<br>ESD |  |  |  |  |  |  |

| LM2904               |                             |                 |  |  |  |  |  |  |

| LM2904A              | /                           |                 |  |  |  |  |  |  |

| LM2904W              |                             | /               |  |  |  |  |  |  |

| LM2904AW             | 1                           | 1               |  |  |  |  |  |  |

| R                    | elated products                                                         |  |  |  |  |  |

|----------------------|-------------------------------------------------------------------------|--|--|--|--|--|

| TSB572               | Dual op-amps for low-<br>power consumption<br>(380 µA with 2.5 MHz GBP) |  |  |  |  |  |

| LM2902<br>LM2902W    | Quad op-amps version                                                    |  |  |  |  |  |

| LM2904WH<br>LM2904AH | High temperature<br>version (150 °C)                                    |  |  |  |  |  |

#### TSV992ST

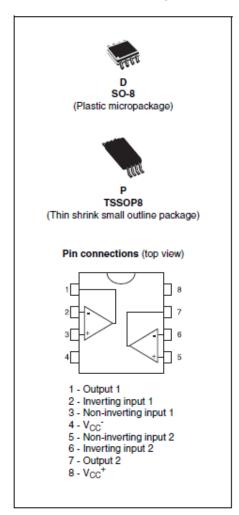

# TSV991, TSV992, TSV994 TSV991A TSV992A, TSV994A

Datasheet

## Rail-to-rail input/output 20 MHz GBP operational amplifiers

#### Features

- Low input offset voltage: 1.5 mV max. (A grade)

- · Rail-to-rail input and output

- Wide bandwidth 20 MHz

- Stable for gain ≥ 4 or ≤ -3

- Low power consumption: 820 µA typ.

- High output current: 35 mA

- Operating from 2.5 V to 5.5 V

- · Low input bias current, 1 pA typ.

- ESD internal protection ≥ 5 kV

#### Applications

- · Battery-powered applications

- Portable devices

- · Signal conditioning and active filtering

- Medical instrumentation

- Automotive applications

## Description

The TSV99x and TSV99xA family of single, dual, and quad operational amplifiers offers low voltage operation and rail-to-rail input and output. These devices feature an excellent speed/power consumption ratio, offering a 20 MHz gain-bandwidth, stable for gains above 4 (100 pF capacitive load), while consuming only 1.1 mA maximum at 5 V. They also feature an ultra-low input bias current. These characteristics make the TSV99x family ideal for sensor interfaces, battery-supplied and portable applications, as well as active filtering. These characteristics make the TSV99x, TSV99xA family ideal for sensor interfaces, battery-supplied and portable applications, as well as active filtering.

#### TSX7192ST

# TSX7192

Low-power, precision, rail-to-rail, 9.0 MHz, 16 V operational amplifiers

Datasheet - production data

#### **Features**

- Low input offset voltage: 200 μV max.

- Rail-to-rail input and output

- Low current consumption: 850 µA max.

- Gain bandwidth product: 9 MHz

- Low supply voltage: 2.7 to 16 V

- Stable when used with Gain ≥ 10

Low input bias current: 50 pA max.

- High ESD tolerance: 4 kV HBM

- Extended temp. range: -40 °C to 125 °C

- Automotive qualification

#### Related products

- See the TSX7191 for single op amp version

- See the TSX712 for lower speeds with similar precision

- See the TSX562 for low-power features

- See the TSX632 for micro-power features

- See the TSX922 for higher speeds

### Applications

- Battery-powered instrumentation

- Instrumentation amplifier

- Active filtering

- High-impedance sensor interface

- Current sensing (high and low side)

## Description

The TSX7192 dual, operational amplifier (op amp) offers high precision functioning with low input offset voltage down to a maximum of 200 µV at 25 °C. In addition, its rail-to-rail input and output functionality allows this product to be used on full range input and output without limitation. This is particularly useful for a low-voltage supply such as 2.7 V that the TSX7192 is able to operate with.

Thus, the TSX7192 has the great advantage of offering a large span of supply voltages, ranging from 2.7 V to 16 V. It can be used in multiple applications with a unique reference.

Low input bias current performance makes the TSX7192 perfect when used for signal conditioning in sensor interface applications. In addition, low-side and high-side current measurements can be easily made thanks to rail-to-rail functionality. The TSX7192 is a decompensated amplifier and must be used with a gain greater than 10 to ensure stability.

High ESD tolerance (4 kV HBM) and a wide temperature range are also good arguments to use the TSX7192 in the automotive market segment.

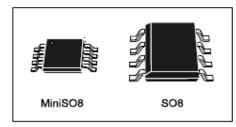

#### PM8834

## PM8834

## 4 A dual low-side MOSFET driver

Datasheet - production data

## Features

- Dual independent low-side MOSFET driver with 4 A sink and source capability

- · Independent enable for each driver

- Driver output parallelability to support higher driving capability

- Matched propagation delays

- CMOS/TTL-compatible input levels

- Wide input supply voltage range: 5 V to 18 V

- Embedded drivers with anti cross conduction protection

- · Low bias switching current

- · Short propagation delays

- Rated for a wide operative temperature range: -40 °C to 125 °C

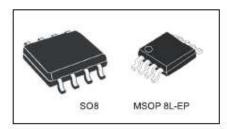

- Industry standard SO8 package and MSOP8 with exposed pad

### Applications

- SMPS

- DC-DC converters

- Motor controllers

- · Line drivers

- · Class-D switching amplifiers

## Description

The PM8834 is a flexible, high-frequency dual low-side driver specifically designed to work with high capacitive MOSFETs and IGBTs.

Both PM8834 outputs can sink and source 4 A independently. A higher driving current can be obtained by connecting the two PWM outputs in parallel

The PM8834 provides two enable pins which can be used to enable the operation of one or both of the output lines.

The PM8834 works with a CMOS/TTL-compatible PWM signal.

The device is available in an SO8 or an MSOP8 package with an exposed pad.

Table 1. Device summary

| Order code | Package     | Packing       |  |

|------------|-------------|---------------|--|

| PM8834     |             | Tube          |  |

| PM8834TR   | S08         | Tape and reel |  |

| PM8834M    | MOOD III ED | Tube          |  |

| PM8834MTR  | MSOP 8L-EP  | Tape and reel |  |

# 4.2 **Construction note**

|                                           |                          |                          |                          |                          | 1                        |

|-------------------------------------------|--------------------------|--------------------------|--------------------------|--------------------------|--------------------------|

|                                           | P/N<br>LM2903WST         | P/N<br>LM2904WST         | P/N<br>TSV992IST         | P/N<br>TSX7192IST        | P/N<br>PM8834            |

| Wafer/Die fab. information                | -                        | <del>-</del>             | <del>-</del>             | <del>-</del>             |                          |

| Wafer fab manufacturing location          | ST Singapore             | ST Singapore             | ST Singapore             | UMC Taiwan               | Catania                  |

| Technology                                | Bipolar                  | Bipolar                  | HF2CMOS                  | HF5CMOS                  | BCD6S                    |

| Die finishing back side                   | RAW SILICON              | RAW SILICON              | RAW SILICON              | RAW SILICON              | CHROMIUM/NICKEL/GOLD     |

| Die size (microns)                        |                          |                          |                          |                          | 989x1058                 |

| Bond pad metallization layers             | AlSiCu                   | AlSiCu                   | AlSiCu                   | AlCu                     | AlCu                     |

| Passivation type                          | Nitride                  | Nitride                  | P-VAPOX/NITRIDE          | PSG + NITRIDE            | TEOS/SiN/Polyimide       |

|                                           | <u> </u>                 | Wafer Testing (EWS       | S) information           | <u>-</u>                 |                          |

| Electrical testing manufacturing location | ST Singapore             |

|                                           | -                        | Assembly info            | rmation                  | <u>-</u>                 |                          |

| Assembly site                             | TSHT                     | TSHT                     | TSHT                     | TSHT                     | TSHT                     |

| Package description                       | MiniSO8                  | MiniSO8                  | MiniSO8                  | MiniSO8                  | MiniSO8                  |

| Molding compound                          | Hitachi CEL-9220         |

| Frame material                            | Cu                       | Cu                       | Cu                       | Cu                       | Cu                       |

| Die attach process                        | Epoxy Glue               |

| Die attach material                       | Henkel 8200T             | Henkel 8200T             | Henkel 8200T             | Henkel 8200T             | Henkel 8600              |

| Wire bonding process                      | Thermosonic ball bonding |

| Wires bonding materials/diameters         | Cu 1 mil Pd Coated       | Gold 1.3Mil              |

| Lead finishing process                    | electroplating           | electroplating           | electroplating           | electroplating           | electroplating           |

| Lead finishing/bump solder material       | Matte Sn                 |

| Final testing information                 |                          |                          |                          |                          |                          |

| Testing location                          | TSHT                     | TSHT                     | TSHT                     | TSHT                     | TSHT                     |

# **5 TESTS PLAN SUMMARY**

#### Test vehicle 5.1

| Lo<br>t# | Process/ Package  | <b>Product Line</b> | Comments |

|----------|-------------------|---------------------|----------|

| 1        | Bipolar/MiniSO8   | 0193                |          |

| 2        | Bipolar/MiniSO8   | 0358                |          |

| 3        | HF5CMOS/MiniSO8   | V992                |          |

| 4        | HVG8A/MiniSO8     | UY36                |          |

| 5        | BCD6S/MiniSO8ePad | UQ18                |          |

# 5.2 **Test plan summary**

|       |    |                 |                                                                                             |    |        |                              | 1                            | Failure/SS                   |                              |                              |      |

|-------|----|-----------------|---------------------------------------------------------------------------------------------|----|--------|------------------------------|------------------------------|------------------------------|------------------------------|------------------------------|------|

| Test  | PC | Std ref.        | Conditions                                                                                  | SS | Steps  | Lot 1<br>0193                | Lot 2<br>0358                | Lot3<br>V992                 | Lot 4<br>UY36                | Lot5<br>UQ18                 | Note |

|       |    |                 | -                                                                                           |    |        |                              |                              |                              |                              |                              |      |

| HTB/  |    | JESD22          |                                                                                             |    | 168 H  | 77                           | 77                           | 77                           | 77                           |                              |      |

| HTOL  | N  | A-108           | Ta = 125°C or $125$ °C, BIAS                                                                |    | 1000 H | 77                           | 77                           | 77                           | 77                           |                              |      |

|       |    |                 |                                                                                             |    | 168 H  | 50                           | 50                           | 50                           | 50                           | 3x50                         |      |

| TIMOT |    | JESD22          | T 1500G                                                                                     |    | 500 H  | 50                           | 50                           | 50                           | 50                           | 3x50                         |      |

| HTSL  | N  | A-103           | Ta = 150°C                                                                                  |    | 1000 H | 50                           | 50                           | 50                           | 50                           | 3x50                         |      |

|       |    |                 |                                                                                             |    |        |                              |                              |                              |                              |                              |      |

|       |    |                 |                                                                                             |    | -      |                              |                              | -                            | •                            |                              | -    |

| PC    |    | JESD22<br>A-113 | Drying 24 H @ 125°C<br>Store 168 H @ Ta=85°C Rh=85%<br>Over Reflow @ Tpeak=260°C 3<br>times |    | Final  | Below<br>sample +<br>22units |      |

| UHAST | Y  | JESD22<br>A-102 | 85%RH / Ta=130°C                                                                            |    | 96 H   | 77                           | 77                           | 77                           | 77                           | 3x77                         |      |

|       |    |                 |                                                                                             |    | 100 cy | 77                           | 77                           | 77                           | 77                           | 3x77                         |      |

| TC    | Y  | JESD22          | T 55°C t- 150°C                                                                             |    | 200 cy | 77                           | 77                           | 77                           | 77                           | 3x77                         |      |

| iC    | ĭ  | A-104           | $Ta = -55^{\circ}C \text{ to } 150^{\circ}C$                                                |    | 500 cy | 77                           | 77                           | 77                           | 77                           | 3x77                         |      |

|       |    |                 |                                                                                             |    | 1000cy | 77                           | 77                           | 77                           | 77                           | 3x77                         |      |

|       |    | JESD22          |                                                                                             |    | 168 H  | 77                           | 77                           | 77                           | 77                           | •                            |      |

| THB   | Y  | A-101           | $Ta = 85^{\circ}C, RH = 85\%, BIAS$                                                         |    | 500 H  | 77                           | 77                           | 77                           | 77                           |                              |      |

|       |    | 71 101          |                                                                                             |    | 1000 H | 77                           | 77                           | 77                           | 77                           |                              |      |

# **6** ANNEXES

# 6.1 **Tests Description**

| Test name                                                                            | Description                                                                                                                                                                                                                                              | Purpose                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

|--------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Die Oriented                                                                         |                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

| HTOL High Temperature Operating Life  HTB High Temperature Bias                      | The device is stressed in static or dynamic configuration, approaching the operative max. absolute ratings in terms of junction temperature and bias condition.                                                                                          | To determine the effects of bias conditions and temperature on solid state devices over time. It simulates the devices' operating condition in an accelerated way.  The typical failure modes are related to, silicon degradation, wire-bonds degradation, oxide faults.                                                                                                                         |  |  |  |  |  |  |

| HTRB High Temperature Reverse Bias  HTFB / HTGB High Temperature Forward (Gate) Bias | The device is stressed in static configura-<br>tion, trying to satisfy as much as possible<br>the following conditions:<br>low power dissipation;<br>max. supply voltage compatible with diffu-<br>sion process and internal circuitry limita-<br>tions; | To determine the effects of bias conditions and temperature on solid state devices over time. It simulates the devices' operating condition in an accelerated way.  To maximize the electrical field across either reverse-biased junctions or dielectric layers, in order to investigate the failure modes linked to mobile contamination, oxide ageing, layout sensitivity to surface effects. |  |  |  |  |  |  |

| HTSL<br>High Temperature<br>Storage Life                                             | The device is stored in unbiased condition at<br>the max. temperature allowed by the pack-<br>age materials, sometimes higher than the<br>max. operative temperature.                                                                                    | To investigate the failure mechanisms activated by high temperature, typically wirebonds solder joint ageing, data retention faults, metal stress-voiding.                                                                                                                                                                                                                                       |  |  |  |  |  |  |

| ELFR<br>Early Life Failure<br>Rate                                                   | The device is stressed in biased conditions at the max junction temperature.                                                                                                                                                                             | To evaluate the defects inducing failure in early life.                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| Package Oriented                                                                     |                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

| PC<br>Preconditioning                                                                | The device is submitted to a typical temperature profile used for surface mounting devices, after a controlled moisture absorption.                                                                                                                      | As stand-alone test: to investigate the moisture sensitivity level. As preconditioning before other reliability tests: to verify that the surface mounting stress does not impact on the subsequent reliability performance. The typical failure modes are "pop corn" effect and delamination.                                                                                                   |  |  |  |  |  |  |

| AC<br>Auto Clave (Pressure Pot)                                                      | The device is stored in saturated steam, at fixed and controlled conditions of pressure and temperature.                                                                                                                                                 | To investigate corrosion phenomena affecting die or package materials, related to chemical contamination and package hermeticity.                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

| TC<br>Temperature Cy-<br>cling                                                       | The device is submitted to cycled temperature excursions, between a hot and a cold chamber in air atmosphere.                                                                                                                                            | To investigate failure modes related to the thermo-mechanical stress induced by the different thermal expansion of the materials interacting in the die-package system. Typical failure modes are linked to metal displacement, dielectric cracking, molding compound delamination, wire-bonds failure, die-attach layer degradation.                                                            |  |  |  |  |  |  |

| Test name                                                | Description                                                                                                                                                                                      | Purpose                                                                                                                                                                                                                                                                                                                               |

|----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TF / IOL Thermal Fatigue / Intermittent Oper- ating Life | The device is submitted to cycled temperature excursions generated by power cycles (ON/OFF) at T ambient.                                                                                        | To investigate failure modes related to the thermo-mechanical stress induced by the different thermal expansion of the materials interacting in the die-package system. Typical failure modes are linked to metal displacement, dielectric cracking, molding compound delamination, wire-bonds failure, die-attach layer degradation. |

| <b>THB</b> Temperature Humidity Bias                     | The device is biased in static configuration<br>minimizing its internal power dissipation,<br>and stored at controlled conditions of ambi-<br>ent temperature and relative humidity.             | To evaluate the package moisture resistance with electrical field applied, both electrolytic and galvanic corrosion are put in evidence.                                                                                                                                                                                              |

| Other                                                    |                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                       |

| ESD<br>Electro Static Dis-<br>charge                     | The device is submitted to a high voltage peak on all his pins simulating ESD stress according to different simulation models. CBM: Charged Device Model HBM: Human Body Model MM: Machine Model | To classify the device according to his susceptibility to damage or degradation by exposure to electrostatic discharge.                                                                                                                                                                                                               |

| LU<br>Latch-Up                                           | The device is submitted to a direct current forced/sunk into the input/output pins. Removing the direct current no change in the supply current must be observed.                                | To verify the presence of bulk parasitic effect inducing latch-up.                                                                                                                                                                                                                                                                    |