**General Purpose Analog & RF Division**

**Power Management**

**Quality and Reliability**

REL. 6088-058-W-2016

# **Reliability Report**

# **New Product Qualification**

HBIP40 Technology Introduction for the 5V and 3.3V Output Voltage versions of the L78L Product Family

Test Vehicles:

L78L05CD13TR L78L05CD13TR L78L33ABUTR

| General                    | Information                                                             |                           | Locations                                    |

|----------------------------|-------------------------------------------------------------------------|---------------------------|----------------------------------------------|

| Product Line               | LA0501<br>LA0501<br>LA3301                                              | Wafer fab                 | Singapore Ang Mo Kio                         |

| Product Description        | 5V 100mA Pos. Reg<br>5V 100mA Pos. Reg.<br>Adjustable voltage regulator | Assembly plant            | SO 08 Shenzhen B/E<br>SOT 89 NANTONG FUJITSU |

| P/N                        | L78L05CD13TR<br>L78L05CD13TR<br>L78L33ABUTR                             | Reliability Lab           | ADG Catania Reliability Lab                  |

| Product Group              | AMG (Analog & MEMS Group)                                               |                           |                                              |

| Product division           | General Purpose Analog & RF<br>Division<br>Power Management             | Reliability<br>assessment | Pass                                         |

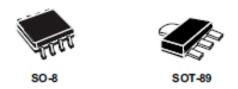

| Package                    | SO 08, Cu wire<br>SOT 89, Au wire                                       |                           |                                              |

| Silicon Process technology | Bip HF - HBIP40V                                                        |                           |                                              |

#### DOCUMENT INFORMATION

| [ | Version | Date       | Pages | Prepared by | Approved by     | Comment      |

|---|---------|------------|-------|-------------|-----------------|--------------|

|   | 1.0     | March 2016 | 7     | Alfio Rao   | Giovanni Presti | Final report |

Note: This report is a summary of the reliability trials performed in good faith by STMicroelectronics in order to evaluate the potential reliability risks during the product life using a set of defined test methods.

This report does not imply for STMicroelectronics expressly or implicitly any contractual obligations other than as set forth in STMicroelectronics general terms and conditions of Sale. This report and its contents shall not be disclosed to a third party without previous written agreement from STMicroelectronics.

**General Purpose Analog & RF Division**

**Power Management**

**Quality and Reliability**

REL. 6088-058-W-2016

#### TABLE OF CONTENTS

| 1 | APPLICABLE AND REFERENCE DOCUMENTS | . 3 |

|---|------------------------------------|-----|

| 2 | GLOSSARY                           | .3  |

|   | RELIABILITY EVALUATION OVERVIEW    | .3  |

|   | 3.1 OBJECTIVES                     | .3  |

|   | 3.2 CONCLUSION                     | .3  |

| 4 | DEVICE CHARACTERISTICS             | .4  |

|   | 4.1 DEVICE DESCRIPTION             | .4  |

|   | 4.2 CONSTRUCTION NOTE              | .5  |

| 5 | TESTS RESULTS SUMMARY              |     |

|   | 5.1 TEST VEHICLE                   | .6  |

|   | 5.2 TEST PLAN AND RESULTS SUMMARY  | .6  |

| 6 | TESTS DESCRIPTION                  | .7  |

**General Purpose Analog & RF Division**

**Power Management**

**Quality and Reliability**

REL. 6088-058-W-2016

#### **1** APPLICABLE AND REFERENCE DOCUMENTS

| Document reference | Short description                                       |

|--------------------|---------------------------------------------------------|

| JESD47             | Stress-Test-Driven Qualification of Integrated Circuits |

#### 2 GLOSSARY

| DUT | Device Under Test |

|-----|-------------------|

| SS  | Sample Size       |

## **<u>3 RELIABILITY EVALUATION OVERVIEW</u>**

#### 3.1 Objectives

Linear Voltage Regulators: HBIP40 Technology Introduction for the 5V and 3.3V Output Voltage versions of the L78L Product Family

Test Vehicles:

| • | L78L05CD13TR | SO 08 Cu Wire  | 1 <sup>st</sup> diff. Lot |

|---|--------------|----------------|---------------------------|

| • | L78L05CD13TR | SO 08 Cu Wire  | 2 <sup>nd</sup> diff. Lot |

| • | L78L33ABUTR  | SOT 89 Au Wire | 3 <sup>rd</sup> diff. Lot |

HBIP40 is a technology already qualified by STM

#### 3.2 Conclusion

Qualification Plan requirements have been fulfilled without exception. It is stressed that reliability tests have shown that the devices behave correctly against environmental tests (no failure). Moreover, the stability of electrical parameters during the accelerated tests demonstrates the ruggedness of the products and safe operation, which is consequently expected during their lifetime.

AMG (Analog & MEMS Group) General Purpose Analog & RF Division Power Management

**Quality and Reliability**

REL. 6088-058-W-2016

## 4 DEVICE CHARACTERISTICS

#### 4.1 Device description

The L78L series of three-terminal positive regulators employ internal current limiting and thermal shutdown, making them essentially indestructible. If adequate heat-sink is provided, they can deliver up to 100 mA output current. They are intended as fixed voltage regulators in a wide range of applications including local or oncard regulation for elimination of noise and distribution problems associated with single-point regulation. In addition, they can be used with power pass elements to make high-current voltage regulators. The L78L series used as Zener diode/resistor combination replacement, offers e improvement along with lower quiescent current and lower noise.

**General Purpose Analog & RF Division**

**Power Management**

**Quality and Reliability**

REL. 6088-058-W-2016

# 4.2 Construction note

|                                           | L78L05CD13TR<br>(1 <sup>st</sup> Lot - HBIP40) | L78L05CD13TR<br>(2 <sup>nd</sup> Lot - HBIP40) | L78L33ABUTR<br>(3 <sup>nd</sup> Lot - HBIP40) |  |  |  |

|-------------------------------------------|------------------------------------------------|------------------------------------------------|-----------------------------------------------|--|--|--|

| Wafer/Die fab. information                |                                                |                                                |                                               |  |  |  |

| Wafer fab manufacturing location          | Singapore Ang Mo Kio                           |                                                |                                               |  |  |  |

| Technology                                |                                                | Bip HF                                         |                                               |  |  |  |

| Process family                            |                                                | HBIP40V                                        |                                               |  |  |  |

| Die finishing back side                   |                                                | LAPPED SILICON                                 |                                               |  |  |  |

| Die size                                  |                                                | 766 x 706 micron                               |                                               |  |  |  |

| Passivation type                          |                                                | P-VAPOX/NITRIDE                                |                                               |  |  |  |

| Wafer Testing (EWS) information           |                                                |                                                |                                               |  |  |  |

| Electrical testing manufacturing location |                                                | Ang Mo Kio EWS                                 |                                               |  |  |  |

| Tester                                    |                                                | ETS 300                                        |                                               |  |  |  |

| Tester Program                            | LA05QAE01 LA05QAE01 LA33QAE01                  |                                                |                                               |  |  |  |

| Assembly information                      |                                                |                                                |                                               |  |  |  |

| Assembly site                             | Shenzhen B/E                                   | Shenzhen B/E                                   | NANTONG<br>FUJITSU                            |  |  |  |

| Package description                       | SO 08                                          | SO 08                                          | SOT 89                                        |  |  |  |

| Molding compound                          | Epoxy                                          | Epoxy                                          | Epoxy                                         |  |  |  |

| Frame material                            | SO 8L 94x125 SHD<br>OpB 4+2+2 4Layers          | SO 8L 94x125 SHD<br>OpB 4+2+2 4Layers          | SOT89-<br>3A/75*70mil                         |  |  |  |

| Die attach material                       | GLUE                                           | GLUE                                           | GLUE                                          |  |  |  |

| Wires bonding materials/diameters         | 1.0 mils - Cu 1.0 mils - Cu 1,0 mils           |                                                |                                               |  |  |  |

| Final testing information                 |                                                |                                                |                                               |  |  |  |

| Testing location                          | ST Shenzhen ST Shenzhen B/E                    |                                                | NANTONG<br>FUJITSU                            |  |  |  |

| Tester                                    | ASL1000 / qt200                                | ASL1000                                        | ASL1000                                       |  |  |  |

| Test Program                              | L78L05C.prg /<br>LAXXFC05.CTS                  |                                                |                                               |  |  |  |

**General Purpose Analog & RF Division**

**Power Management**

**Quality and Reliability**

REL. 6088-058-W-2016

## 5 TESTS RESULTS SUMMARY

# 5.1 Test vehicle

| Lot # | Technical Code | Package | Product Line | Comments |

|-------|----------------|---------|--------------|----------|

| 1     | ZPO7*LA05BA6   | SO 08   | LA0501       | HBIP40V  |

| 2     | ZPO7*LA05BA6   | SO 08   | LA0501       | HBIP40V  |

| 3     | 1F39*LA33BA6   | SOT 89  | LA3301       | HBIP40V  |

## 5.2 Test plan and results summary

|         |                    |                           |                                   |    |                  | F            | ailure/S     | S              |                        |

|---------|--------------------|---------------------------|-----------------------------------|----|------------------|--------------|--------------|----------------|------------------------|

| Test    | PC                 | Std ref.                  | Conditions                        | SS | Steps            | Lot 1<br>SO8 | Lot 2<br>SO8 | Lot 3<br>Sot89 | Note                   |

| Die Ori | Die Oriented Tests |                           |                                   |    |                  |              |              |                |                        |

|         |                    | JESD22                    |                                   |    | 168 h            | 0/77         | 0/77         |                |                        |

| HTOL    | Ν                  | A-108                     | Ta = 125°C Vcc= +30V              |    | 500 h            | 0/77         | 0/77         |                |                        |

|         |                    |                           |                                   |    | 1000 h           | 0/77         | 0/77         | 0/15           |                        |

|         |                    | JESD22                    | <b>T</b> (5000                    |    | 168 h            | 0/45         | 0/45         | 0/45           |                        |

| HTSL    | Ν                  | A-103                     | Ta = 150°C                        |    | 500 h            | 0/45         | 0/45         | 0/45           |                        |

|         |                    |                           |                                   |    | 1000 h           | 0/45         | 0/45<br>0/45 | 0/45           |                        |

| HTSL    | Ν                  | JESD22                    | Ta = 175°C                        |    | 168 h<br>500 h   | 0/45<br>0/45 | 0/45         |                | Engineering evaluation |

| I I SL  | IN                 | A-103                     | Ta = 175 C                        |    | 1000 h           | 0/45         | 0/45         |                | on Cu wire             |

| Packag  |                    | riented Tests             |                                   |    | 1000 11          | 0/45         | 0/45         |                |                        |

| i acray |                    |                           | Drying 24 H @ 125°C               |    |                  |              |              |                |                        |

| PC      |                    | JESD22                    | Store 168 H @ Ta=85°C Rh=85%      |    | Final            | Pass         |              | Pass           |                        |

|         |                    | A-113                     | Over Reflow @ Tpeak=260°C 3 times |    |                  |              |              |                |                        |

| AC      | Y                  | JESD22                    | Pa= 2Atm / Ta=121°C               |    | 168 h            | 0/77         | 0/77         | 0/77           |                        |

|         |                    | A-102                     |                                   |    | 100 01           | 0/77         | 0/77         | 0/77           |                        |

| тс      | Y                  | , JESD22                  | Ta = -65°C to 150°C               |    | 100 cy<br>200 cy | 0/77<br>0/77 | 0/77<br>0/77 | 0/77<br>0/77   |                        |

|         | T                  | A-104                     | 1a = -65 C 10 150 C               |    | 200 cy           | 0/77         | 0/77         | 0/77           |                        |

|         |                    |                           |                                   |    | 168 h            | 0/77         | 0/77         | 0/11           |                        |

| TUD     | Y                  | JESD22                    | Ta = 85°C, RH = 85%,              |    |                  |              |              |                |                        |

| THB     | ř                  | A-101                     | A-101 Vcc1= +24V                  |    | 500 h            | 0/77         | 0/77         |                |                        |

| Other T | to                 |                           |                                   |    | 1000 h           | 0/77         | 0/77         |                |                        |

| Other 1 | ests               |                           |                                   | [  | [                | [            |              |                |                        |

| ESD     |                    | ANSI/ESDA/J<br>EDEC JS001 | HBM +/- 2000V                     | 3  | 2KV              | Pass         |              |                |                        |

|         |                    | ANSI/ESD<br>S5.3.1        | CDM 500V                          | 3  | 500V             | Pass         |              |                |                        |

**General Purpose Analog & RF Division**

**Power Management**

**Quality and Reliability**

REL. 6088-058-W-2016

# 6 TESTS DESCRIPTION

| Test name                                  | Description                                                                                                                                                                                | Purpose                                                                                                                                                                                                                                                                                                             |

|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Die Oriented                               |                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                     |

| <b>HTOL</b><br>High Temperature<br>Bias    | The device is stressed in static or dynamic configuration, approaching the operative max. absolute ratings in terms of junction temperature and bias condition.                            | simulates the devices' operating condition in an                                                                                                                                                                                                                                                                    |

| HTSL<br>High Temperature<br>Storage Life   | The device is stored in unbiased condition at the max. temperature allowed by the package materials, sometimes higher than the max. operative temperature.                                 | To investigate the failure mechanisms activated by<br>high temperature, typically wire-bonds solder joint<br>ageing, data retention faults, metal stress-voiding.                                                                                                                                                   |

| Package Oriented                           |                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                     |

| <b>PC</b><br>Preconditioning               |                                                                                                                                                                                            | As stand-alone test: to investigate the moisture<br>sensitivity level.<br>As preconditioning before other reliability tests:<br>to verify that the surface mounting stress does<br>not impact on the subsequent reliability<br>performance.<br>The typical failure modes are "pop corn" effect<br>and delamination. |

| AC<br>Auto Clave<br>(Pressure Pot)         | The device is stored in saturated steam, at fixed<br>and controlled conditions of pressure and<br>temperature.                                                                             | To investigate corrosion phenomena affecting die or                                                                                                                                                                                                                                                                 |

| TC<br>Temperature Cycling                  | The device is submitted to cycled temperature excursions, between a hot and a cold chamber in air atmosphere.                                                                              | To investigate failure modes related to the thermo-<br>mechanical stress induced by the different thermal<br>expansion of the materials interacting in the die-                                                                                                                                                     |

| <b>THB</b><br>Temperature<br>Humidity Bias | The device is biased in static configuration minimizing its internal power dissipation, and stored at controlled conditions of ambient temperature and relative humidity.                  | To evaluate the package moisture resistance with electrical field applied, both electrolytic and galvanic corrosion are put in evidence.                                                                                                                                                                            |

| Other Test                                 |                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                     |

| ESD<br>Electro Static<br>Discharge         | The device is submitted to a high voltage peak<br>on all his pins simulating ESD stress according<br>to different simulation models.<br>CDM: Charged Device Model<br>HBM: Human Body Model | To classify the device according to his susceptibility<br>to damage or degradation by exposure to<br>electrostatic discharge.                                                                                                                                                                                       |